(报告出品方:中信证券)

一、公司概况:全球EDA巨头,产品客户体系完善

1.1 公司概述:全球EDA龙头,业务遍布全球

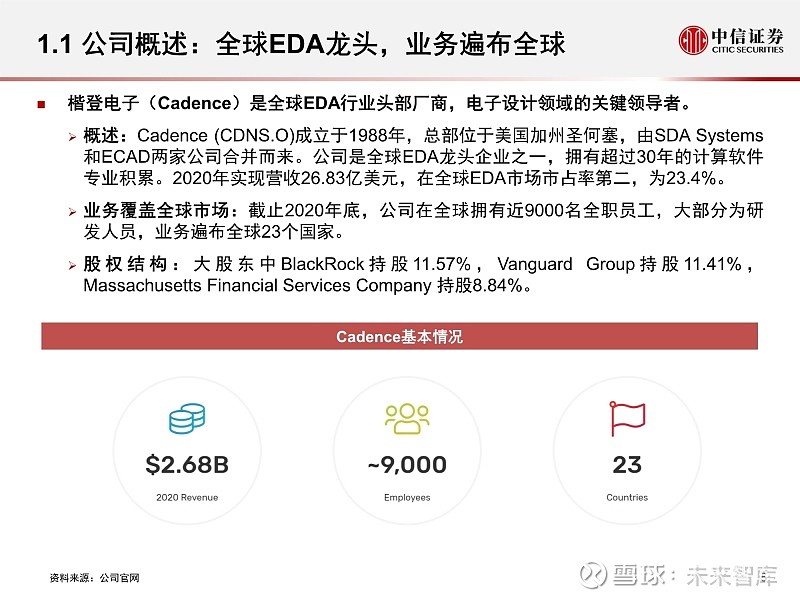

楷登电子(Cadence)是全球EDA行业头部厂商,电子设计领域的关键领导者。

概述:Cadence (CDNS.O)成立于1988年,总部位于美国加州圣何塞,由SDA Systems 和ECAD两家公司合并而来。公司是全球EDA龙头企业之一,拥有超过30年的计算软件 专业积累。2020年实现营收26.83亿美元,在全球EDA市场市占率第二,为23.4%。

1.2 客户生态:客群庞大,强化合作促进产品迭代

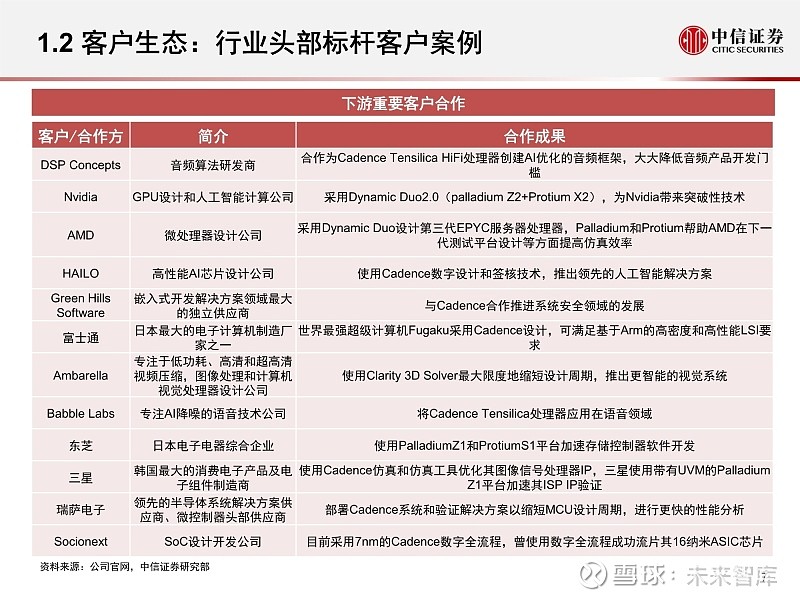

公司客群庞大,与头部客户保持紧密合作,涉及消费电子、超大型计算机、5G通讯、汽 车、航空、工业和医疗等行业,其中大客户包括英伟达、高通、博通、台积电、德州仪器、 意法半导体等。

重视与下游生态合作,促进产品能力提升。Cadence通过长期与台积电、格罗方德、 ARM等全球领先的IC制造和设计企业保持合作,保证自身EDA工具工艺库信息完善,达 到产品随先进工艺演进不断迭代的效果,巩固自身竞争优势。

1.3 管理团队:技术前瞻性强,行业经验丰富

陈立武(Lip-BuTan),CEO(2021年底将转任执行董事长)

工作成就:推动了公司全面转型。在其领导下,Cadence成功推出一系列高度 创新的产品,积极开展战略收购,与市场上领先的客户和生态系统合作伙伴结 成深度互信的伙伴关系。任期内,公司营收从不到10亿美元增加到接近30亿 美元,营业毛利增长超过35%,股价上升超过3200%。

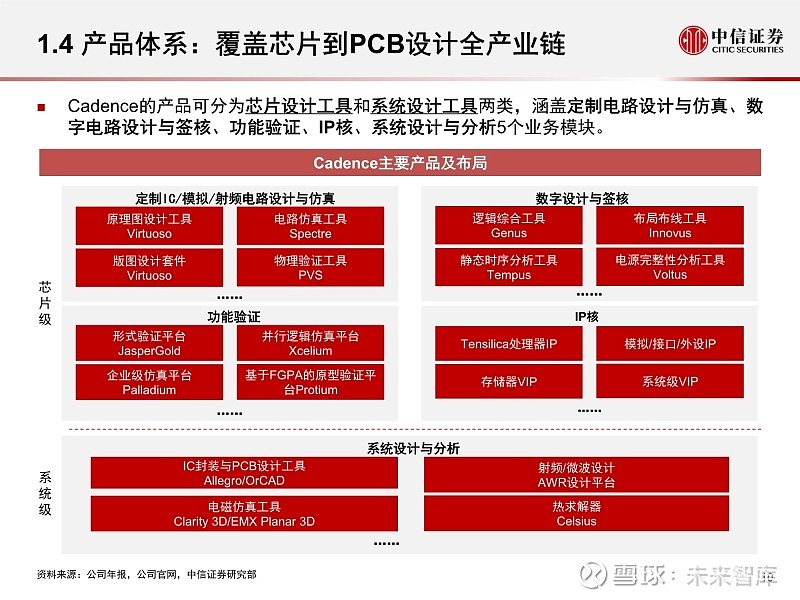

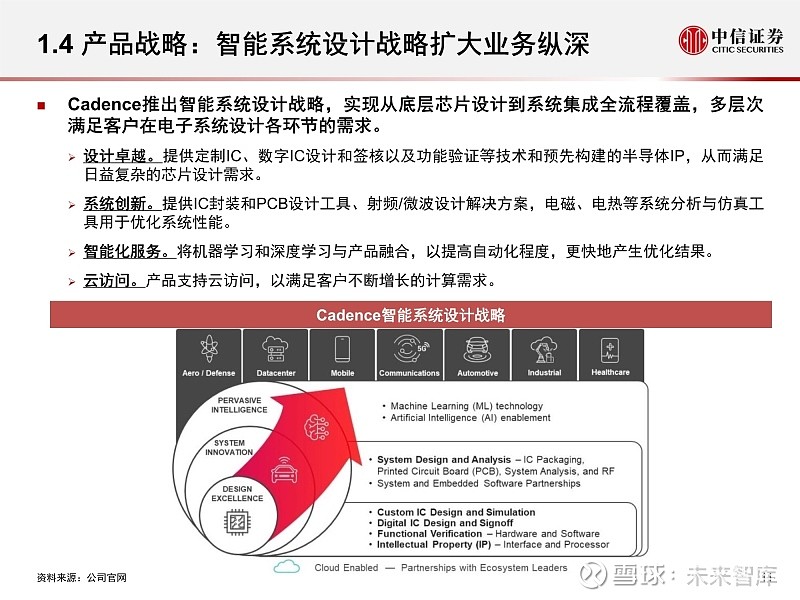

1.4 产品体系:覆盖芯片到PCB设计全产业链

Cadence的产品可分为芯片设计工具和系统设计工具两类,涵盖定制电路设计与仿真、数 字电路设计与签核、功能验证、IP核、系统设计与分析5个业务模块。

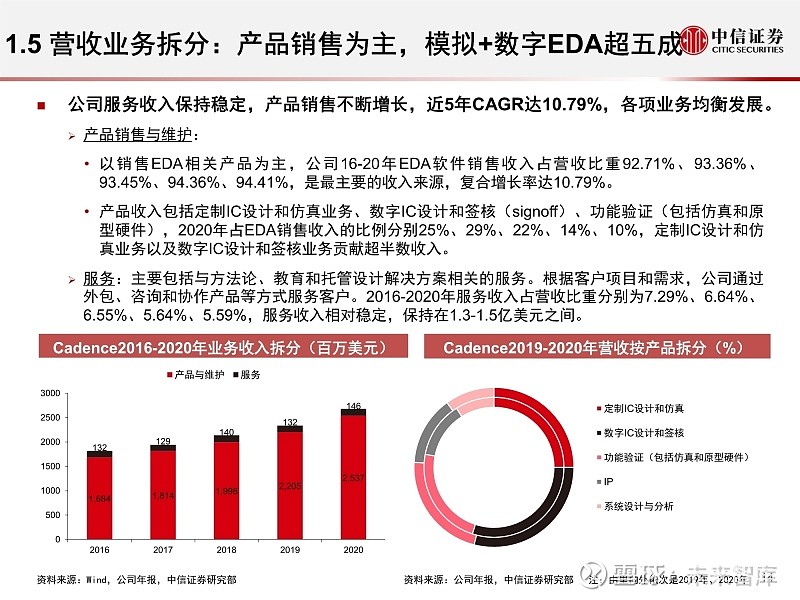

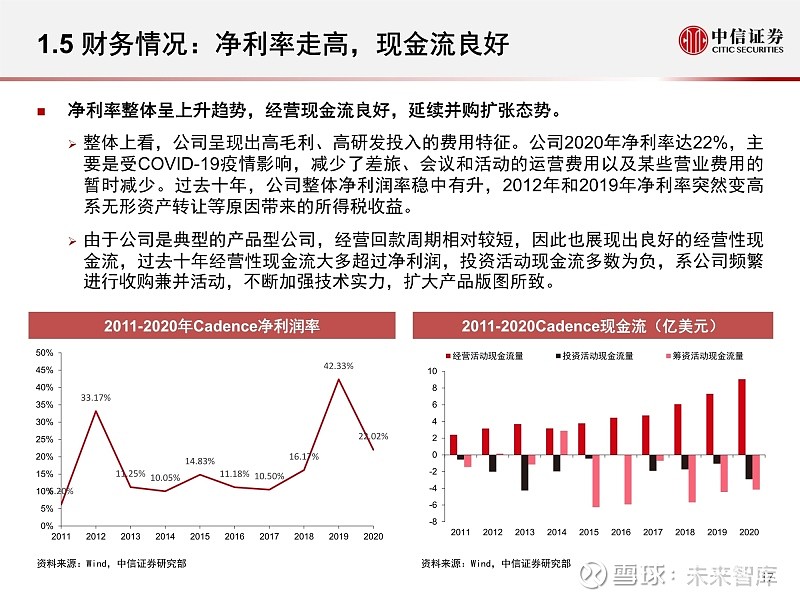

1.5 财务情况:营收稳步增长,利润增速更高

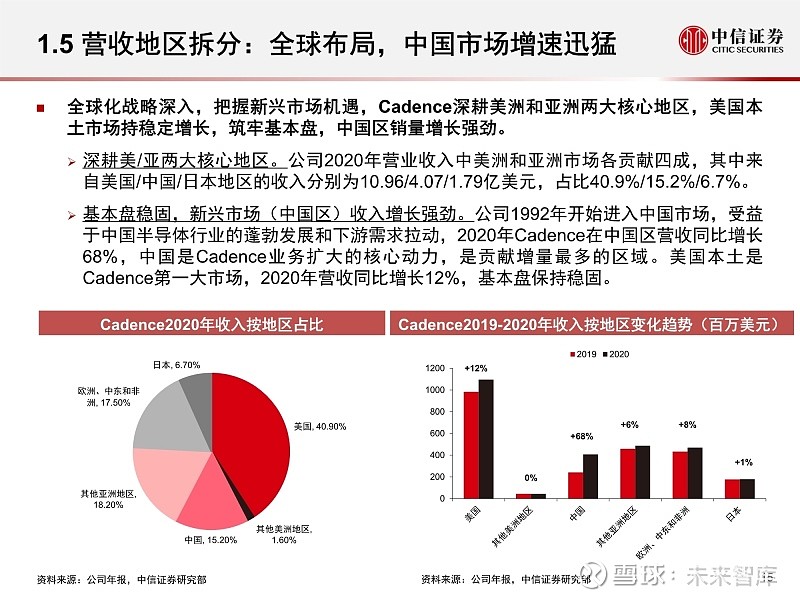

营业收入:2020年收入26.83亿美元,近十年保持稳定增长,2011-2020年CAGR为10%。

公司在18-20年实现营业总收入21.38亿美元、23.36亿美元、26.83亿美元,同比增长10.04%、 9.26%、14.85%,主要由于移动设备、5G、人工智能、区块链等半导体行业下游需求增长的持续拉 动,此外公司在EDA行业的龙头效应也带动了收入的稳定提升。

净利润:2020年归母净利润为5.91亿美元,2011-2020年CAGR为26%。

公司在18-20年实现归母净利润3.46亿美元、9.89亿美元、5.91亿美元,同比增长69.61%、185.84%、 -40.24%,公司净利润呈总体上升态势,近十年CAGR为26.35%。2012年和2019年净利润激增主要 由于无形资产转让带来的所得税收入。

公司与全球头部集成电路设计企业、芯片制造企业等客户建立良好的业务合作关系,并通过持续的 技术优化和产品迭代稳定与深化客户合作,具备较高的盈利能力和持续发展的空间。

(获取优质报告请登录:未来智库)

二、发展历程:自研+并购壮大业务版图

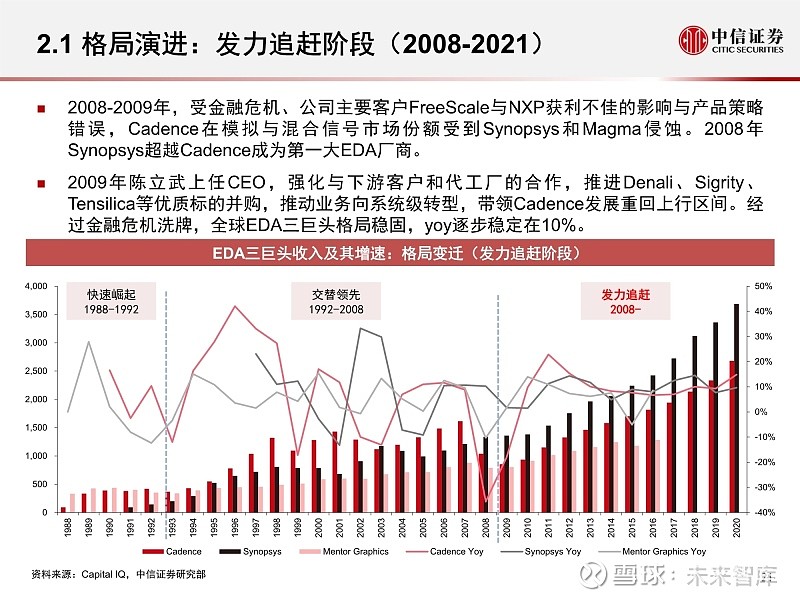

2.1 格局演进

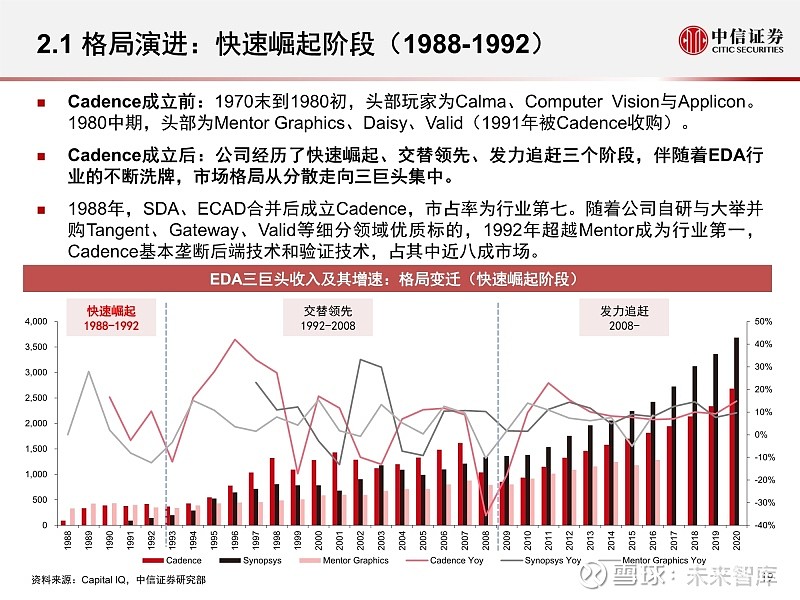

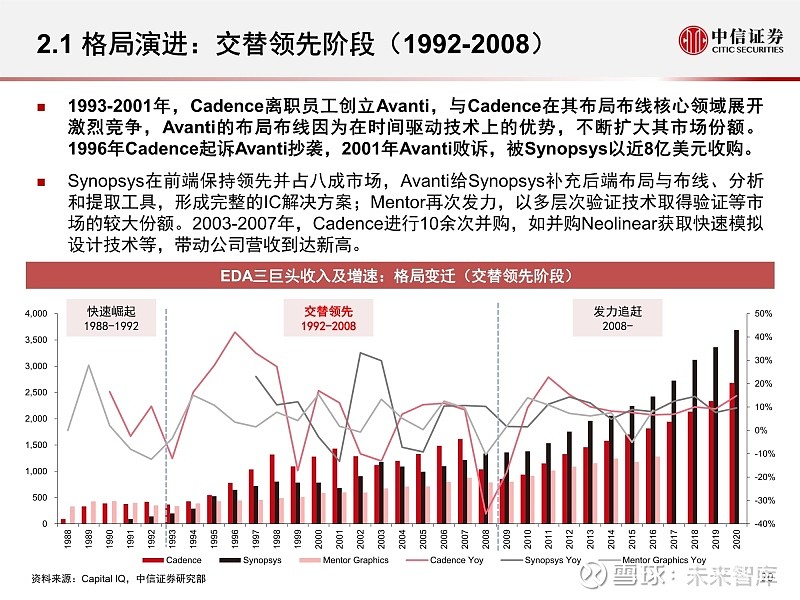

Cadence成立前:1970末到1980初,头部玩家为Calma、Computer Vision与Applicon。 1980中期,头部为Mentor Graphics、Daisy、Valid(1991年被Cadence收购)。

Cadence成立后:公司经历了快速崛起、交替领先、发力追赶三个阶段,伴随着EDA行 业的不断洗牌,市场格局从分散走向三巨头集中。

2.2 发展路径:始于布线验证工具,走向EDA全流程巨头

Cadence的产品体系始于布线验证工具,通过“内生发展+外延并购”的方式,不断补全 自身工具链,最终实现满足各场景应用的EDA闭环解决方案,并向系统设计分析延伸。

2.3 内生动力:保持高研发投入,提升产品竞争力

Cadence保持较高的研发投入,巩固自身基本盘,不断打磨后端布局布线与验证产品, 同时把握行业发展的前沿,不断进行技术预研和推广,积极进行战略转型,使得公司产 品能牢牢抓住市场。

2.4 外延并购:并购扩充产品线,驱动公司成长

Cadence通过大举并购,迅速扩展产品线,夯实产品的技术能力。

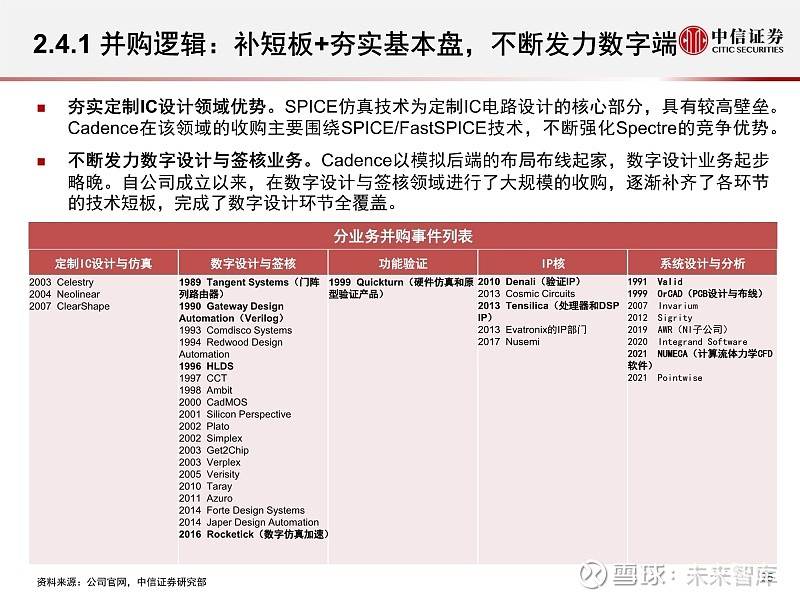

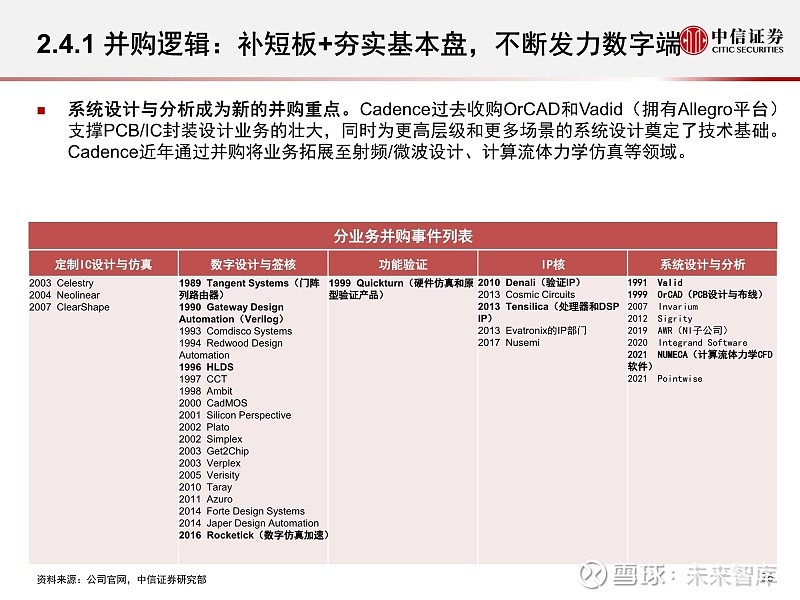

2.4.1 并购逻辑:补短板+夯实基本盘,不断发力数字端

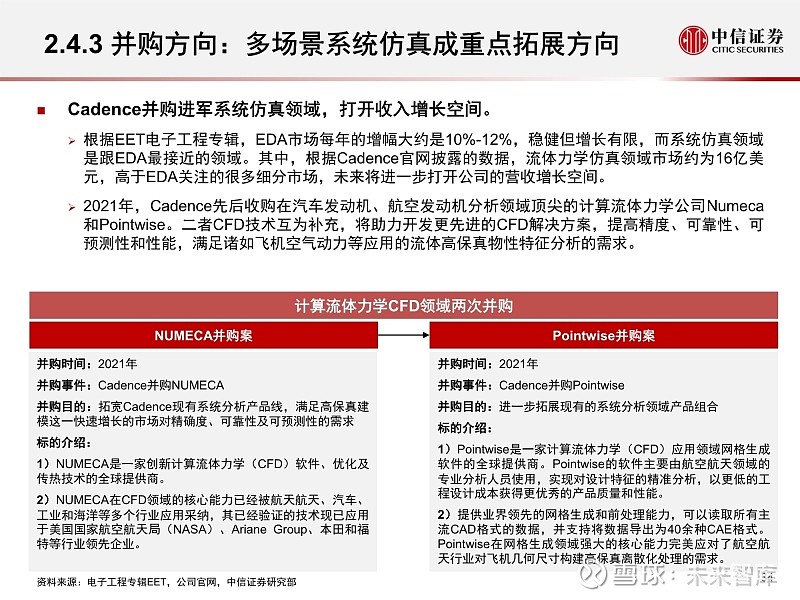

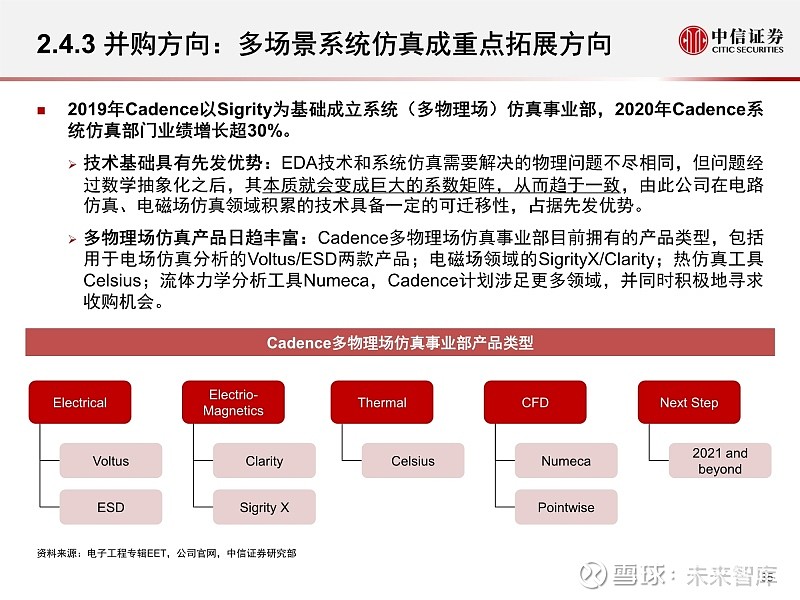

系统设计与分析成为新的并购重点。Cadence过去收购OrCAD和Vadid(拥有Allegro平台) 支撑PCB/IC封装设计业务的壮大,同时为更高层级和更多场景的系统设计奠定了技术基础。 Cadence近年通过并购将业务拓展至射频/微波设计、计算流体力学仿真等领域。

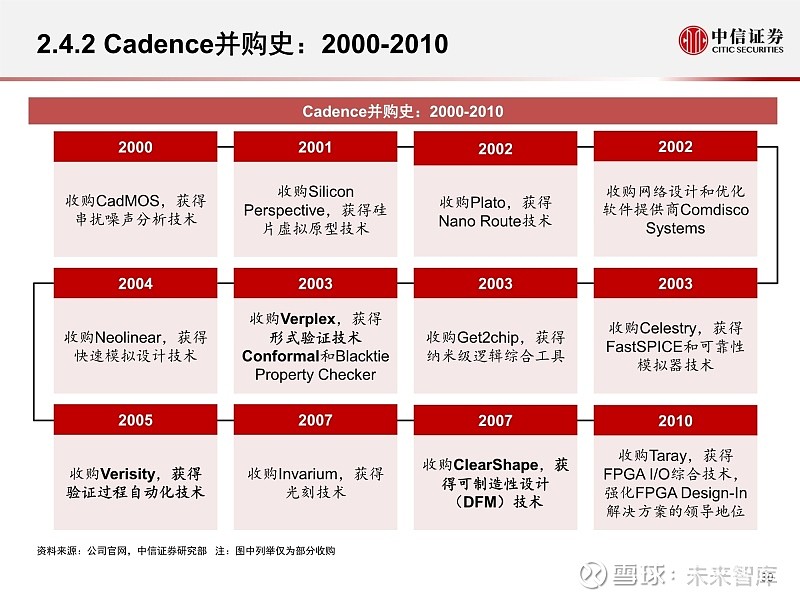

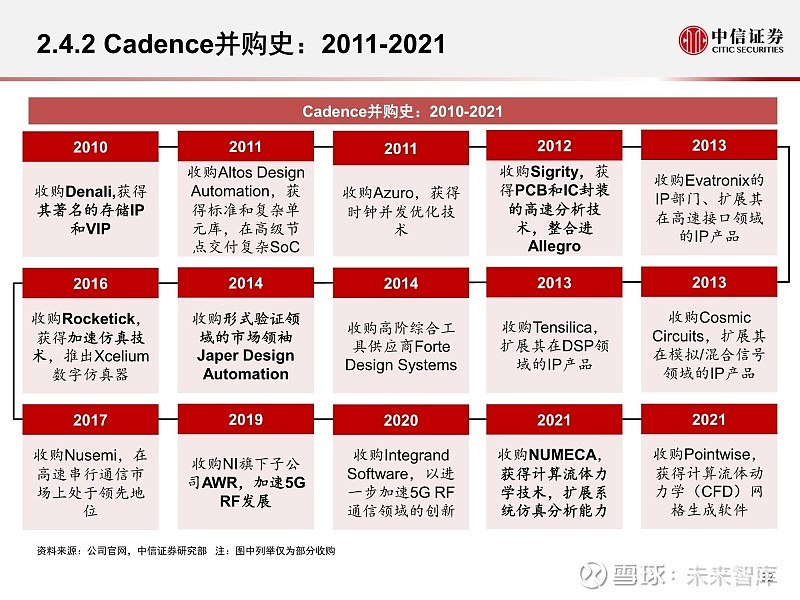

2.4.2 Cadence并购史

并购重点:完善并发展设计工具,从模拟IC设计工具拓展到数字设计,从芯片设计工具拓 展到PCB设计工具。

2.4.3 并购方向:强化射频领域优势,把握5G发展机会

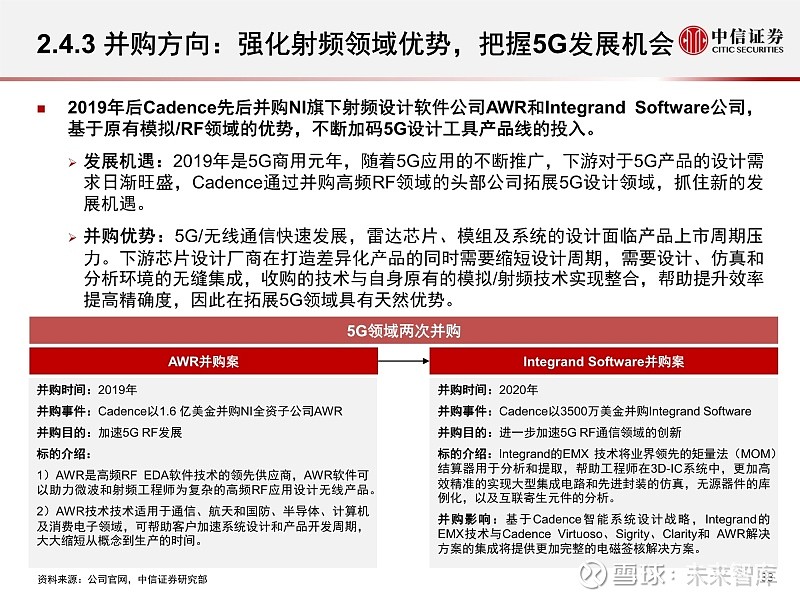

2019年后Cadence先后并购NI旗下射频设计软件公司AWR和Integrand Software公司, 基于原有模拟/RF领域的优势,不断加码5G设计工具产品线的投入。

发展机遇:2019年是5G商用元年,随着5G应用的不断推广,下游对于5G产品的设计需 求日渐旺盛,Cadence通过并购高频RF领域的头部公司拓展5G设计领域,抓住新的发 展机遇。

并购优势:5G/无线通信快速发展,雷达芯片、模组及系统的设计面临产品上市周期压 力。下游芯片设计厂商在打造差异化产品的同时需要缩短设计周期,需要设计、仿真和 分析环境的无缝集成,收购的技术与自身原有的模拟/射频技术实现整合,帮助提升效率 提高精确度,因此在拓展5G领域具有天然优势。

三、产品体系:全流程EDA软件供应商

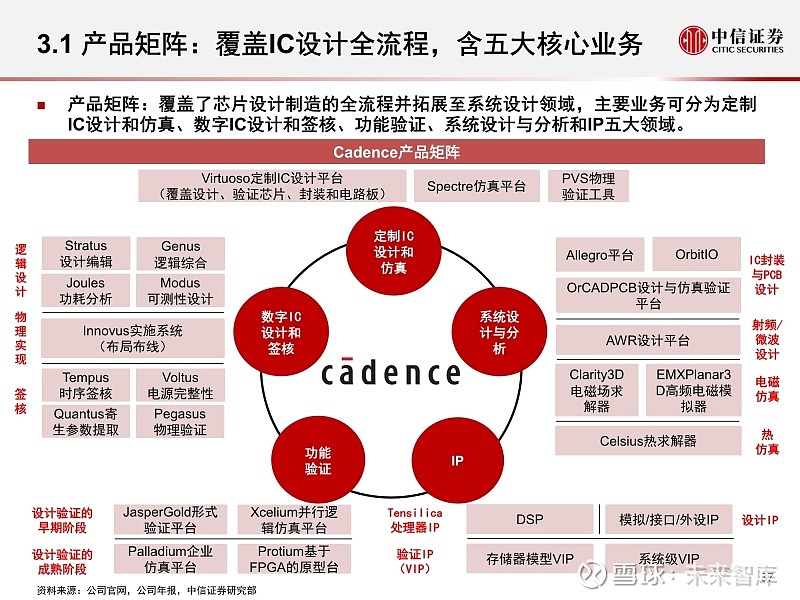

3.1 产品矩阵:覆盖IC设计全流程,含五大核心业务

产品矩阵:覆盖了芯片设计制造的全流程并拓展至系统设计领域,主要业务可分为定制 IC设计和仿真、数字IC设计和签核、功能验证、系统设计与分析和IP五大领域。

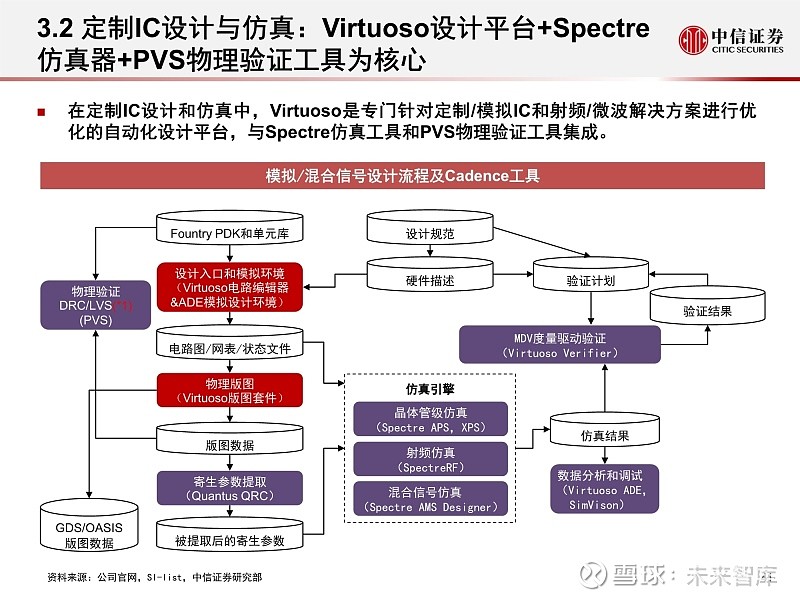

3.2 定制IC设计与仿真:Virtuoso设计平台+Spectre 仿真器+PVS物理验证工具为核心

在定制IC设计和仿真中,Virtuoso是专门针对定制/模拟IC和射频/微波解决方案进行优 化的自动化设计平台,与Spectre仿真工具和PVS物理验证工具集成。

3.2.1 Virtuoso:模拟/混合信号前后端设计的核心平台

Virtuoso是专门针对定制IC/射频/微波的自动化设计平台,支持从芯片设计到高级封装 和PCB布图的整个流程。

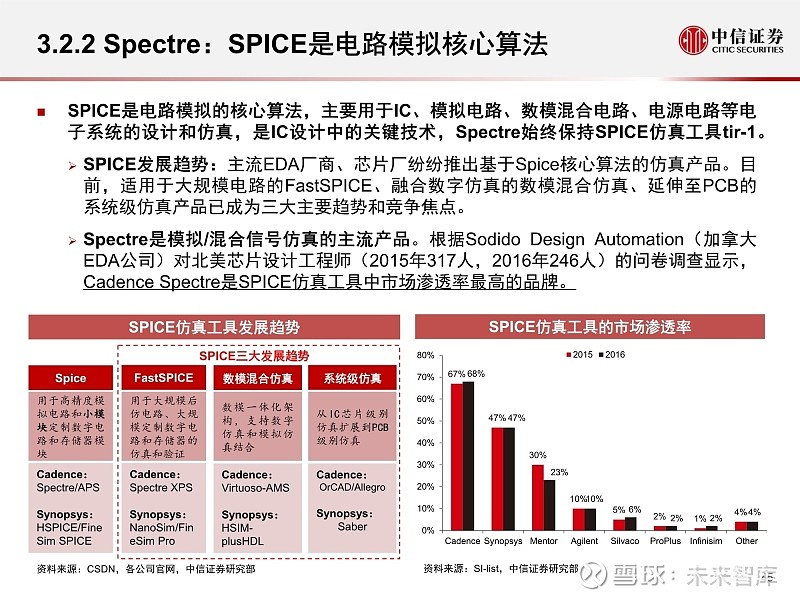

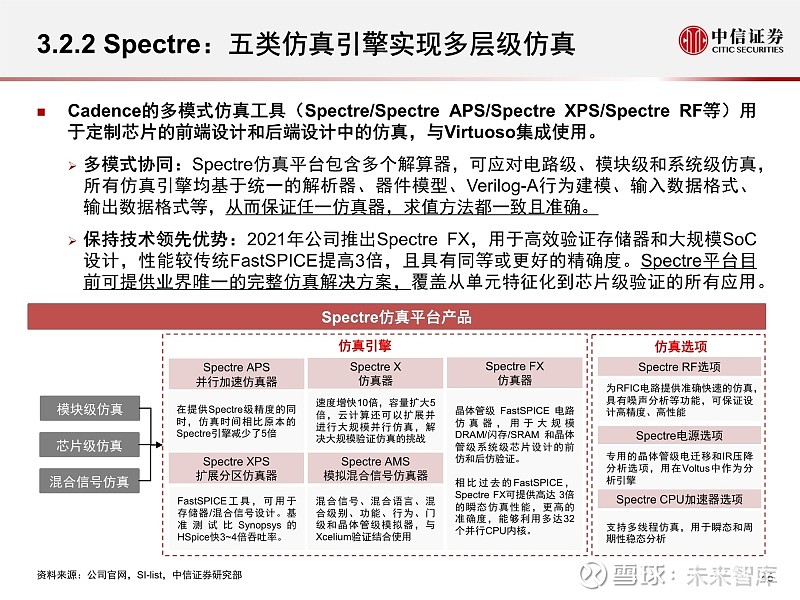

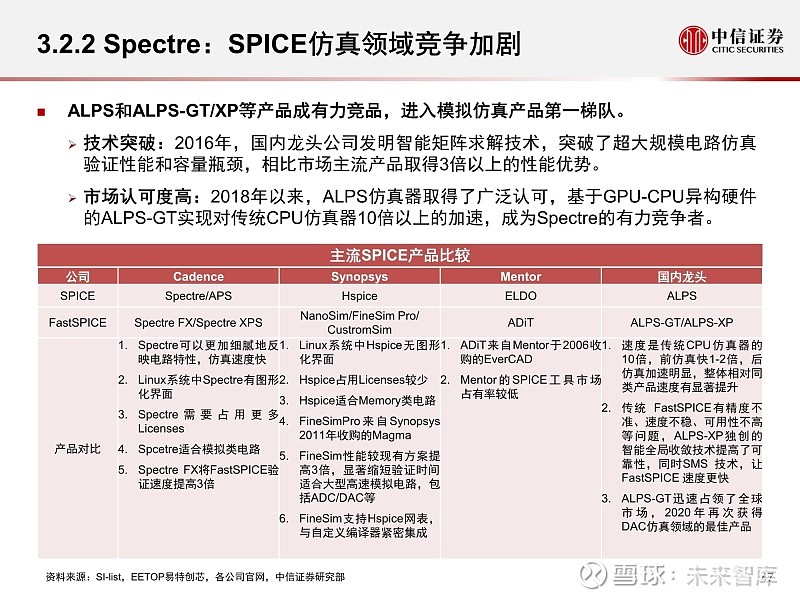

3.2.2 Spectre:SPICE是电路模拟核心算法

SPICE是电路模拟的核心算法,主要用于IC、模拟电路、数模混合电路、电源电路等电 子系统的设计和仿真,是IC设计中的关键技术,Spectre始终保持SPICE仿真工具tir-1。

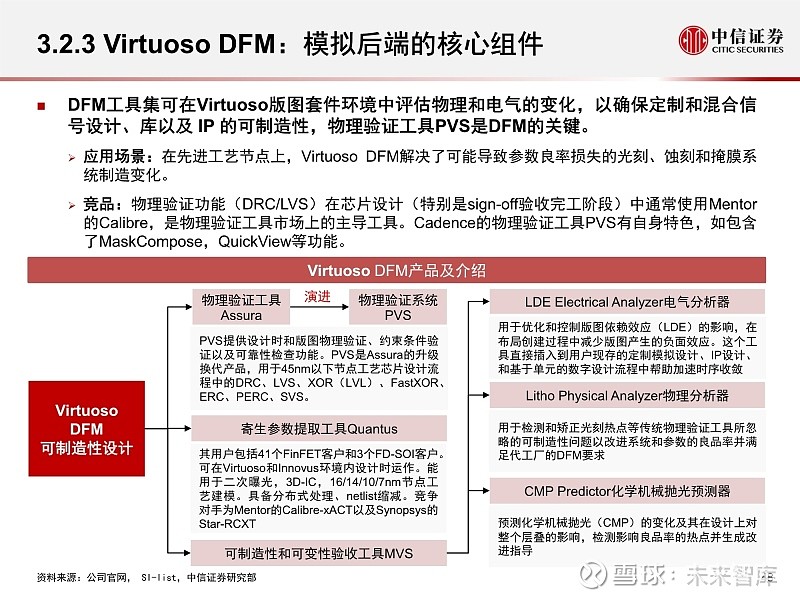

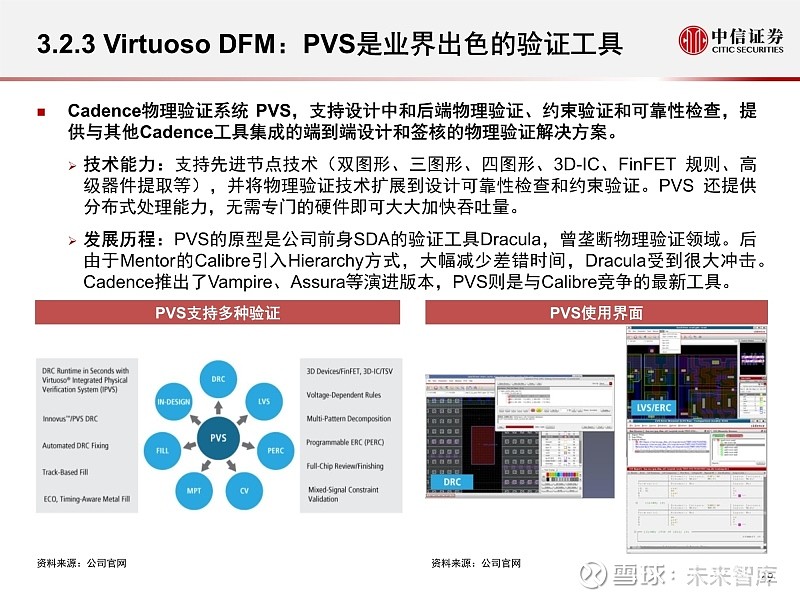

3.2.3 Virtuoso DFM:模拟后端的核心组件

DFM工具集可在Virtuoso版图套件环境中评估物理和电气的变化,以确保定制和混合信 号设计、库以及 IP 的可制造性,物理验证工具PVS是DFM的关键。

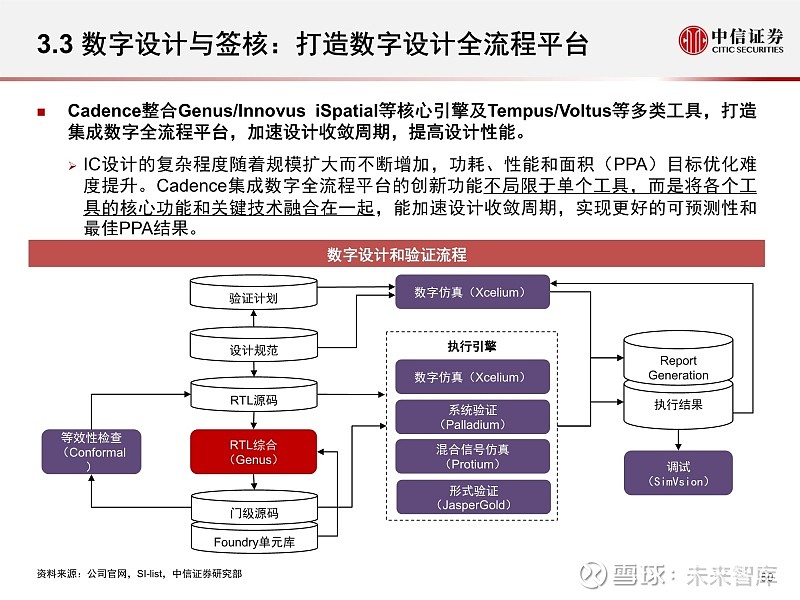

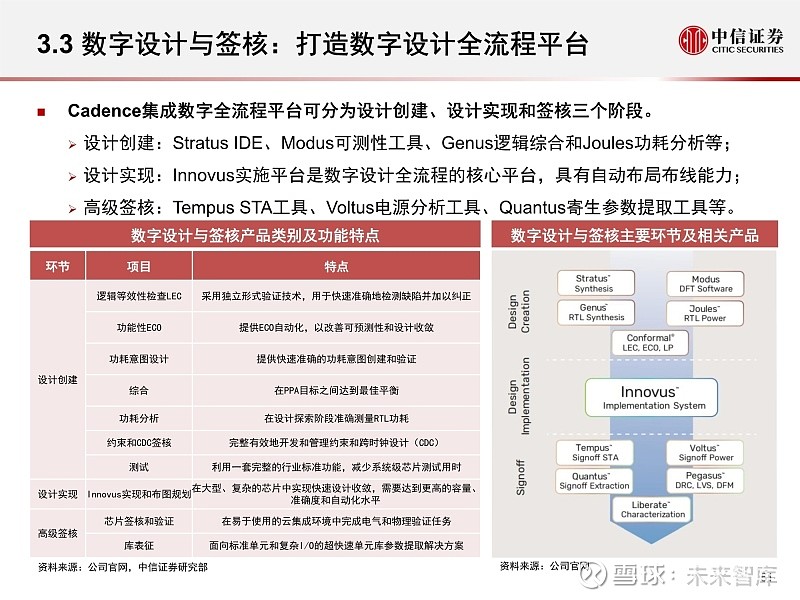

3.3 数字设计与签核:打造数字设计全流程平台

Cadence集成数字全流程平台可分为设计创建、设计实现和签核三个阶段。

设计创建:Stratus IDE、Modus可测性工具、Genus逻辑综合和Joules功耗分析等;

设计实现:Innovus实施平台是数字设计全流程的核心平台,具有自动布局布线能力;

高级签核:Tempus STA工具、Voltus电源分析工具、Quantus寄生参数提取工具等。

3.3.1 Stratus HLS:集成开发平台提升数字设计效率

Stratus HLS是Cadence针对ASIC、SoC、FPGA设计的高阶综合IDE集成开发平台。

3.3.2 DFT:不断追赶Mentor Graphics

Modus是Cadence开发的诊断与测试工具,可做扫描插入、压缩、ATPG(自动测试模 式生成)、逻辑和存储器BIST、PMBIST,压缩比率达400倍。

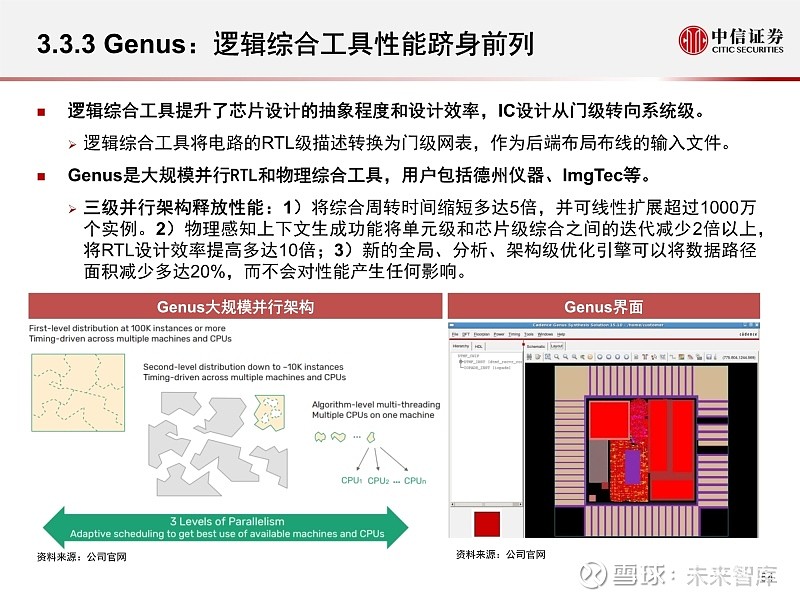

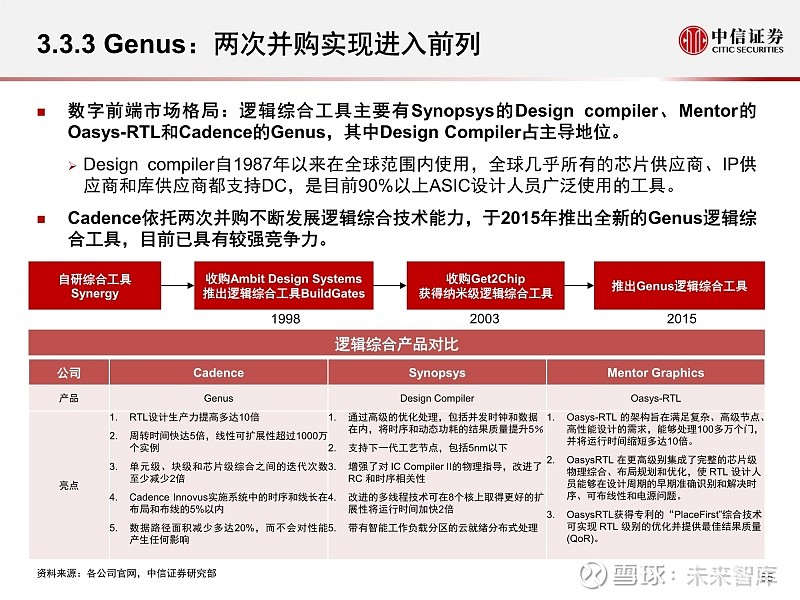

3.3.3 Genus:逻辑综合工具性能跻身前列

逻辑综合工具提升了芯片设计的抽象程度和设计效率,IC设计从门级转向系统级。

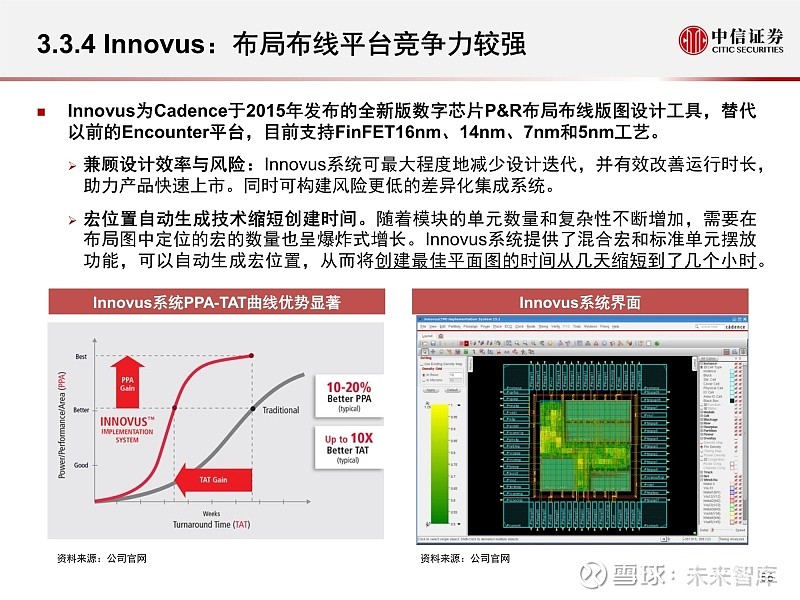

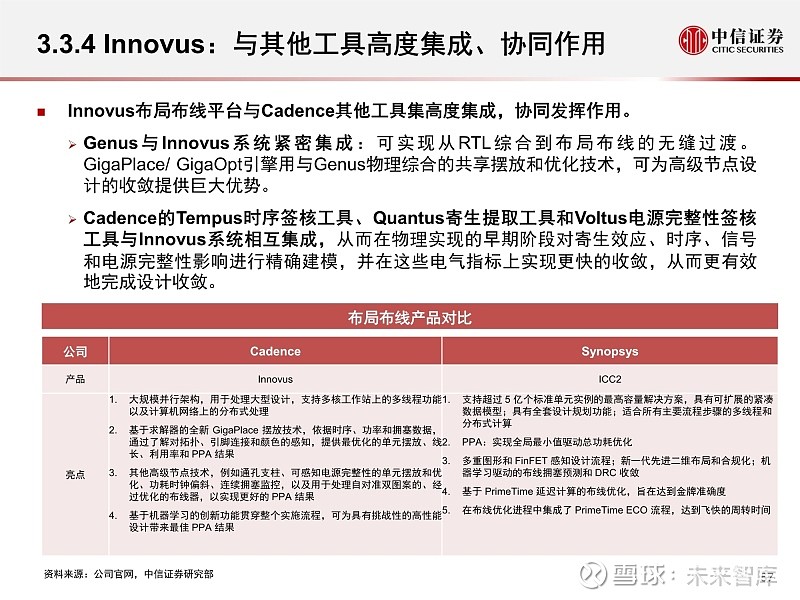

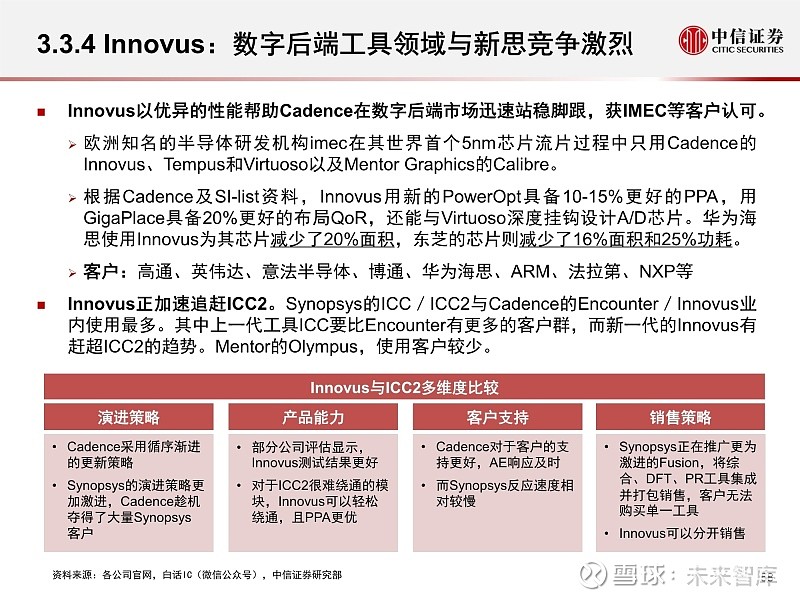

3.3.4 Innovus:布局布线平台竞争力较强

Innovus为Cadence于2015年发布的全新版数字芯片P&R布局布线版图设计工具,替代 以前的Encounter平台,目前支持FinFET16nm、14nm、7nm和5nm工艺。

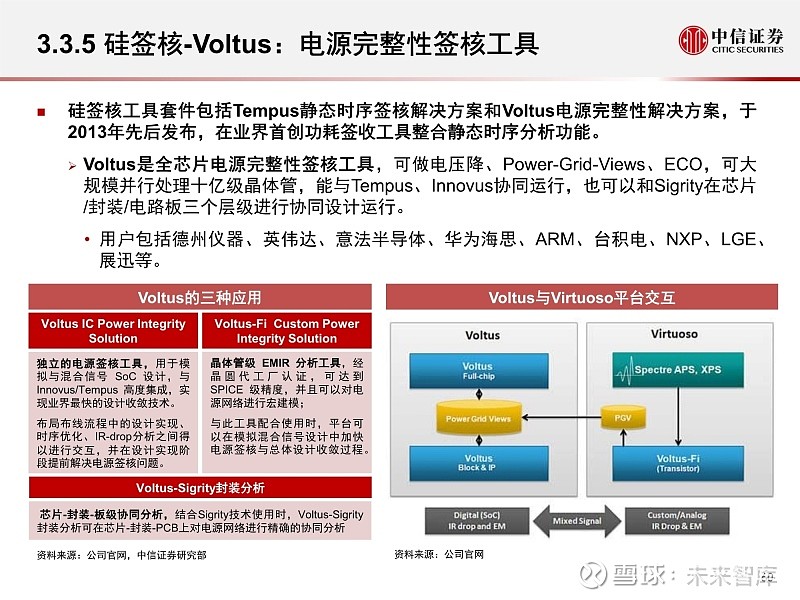

3.3.5 硅签核-Tempus:静态时序签核工具

硅签核工具套件包括Tempus静态时序签核解决方案和Voltus电源完整性解决方案,于 2013年先后发布,在业界首创功耗签收工具整合静态时序分析功能。

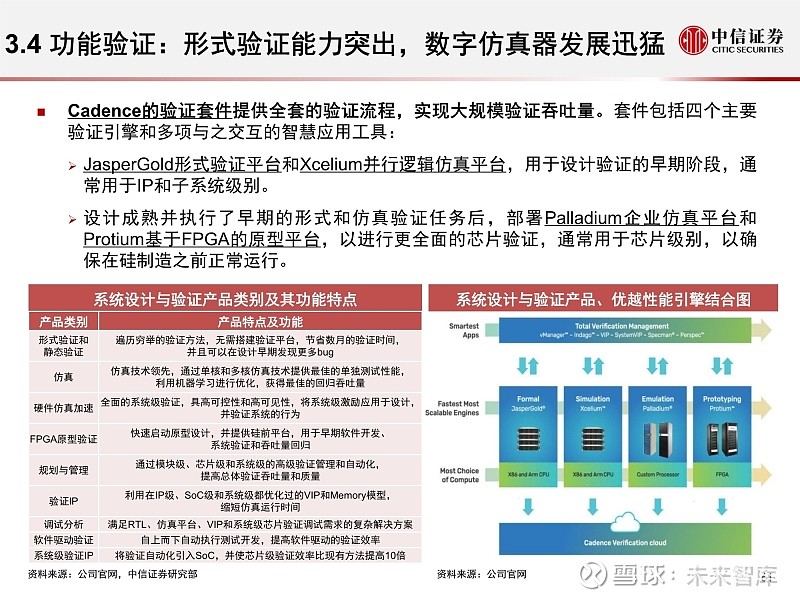

3.4 功能验证:形式验证能力突出,数字仿真器发展迅猛

Cadence的验证套件提供全套的验证流程,实现大规模验证吞吐量。

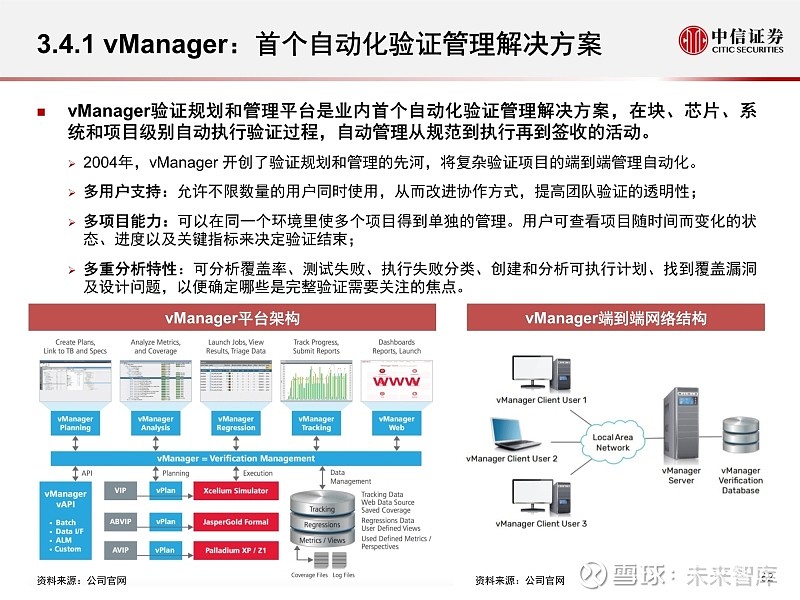

3.4.1 vManager:首个自动化验证管理解决方案

vManager验证规划和管理平台是业内首个自动化验证管理解决方案,在块、芯片、系 统和项目级别自动执行验证过程,自动管理从规范到执行再到签收的活动。

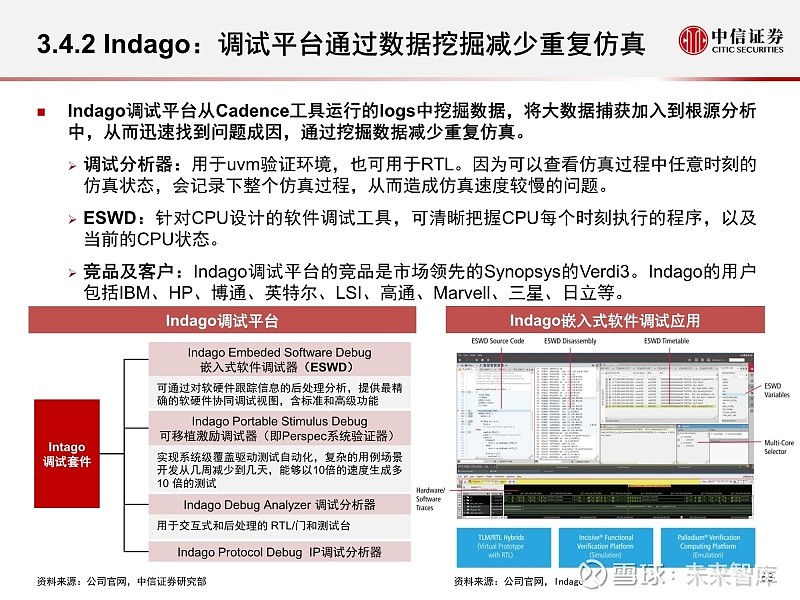

3.4.2 Indago:调试平台通过数据挖掘减少重复仿真

Indago调试平台从Cadence工具运行的logs中挖掘数据,将大数据捕获加入到根源分析 中,从而迅速找到问题成因,通过挖掘数据减少重复仿真。

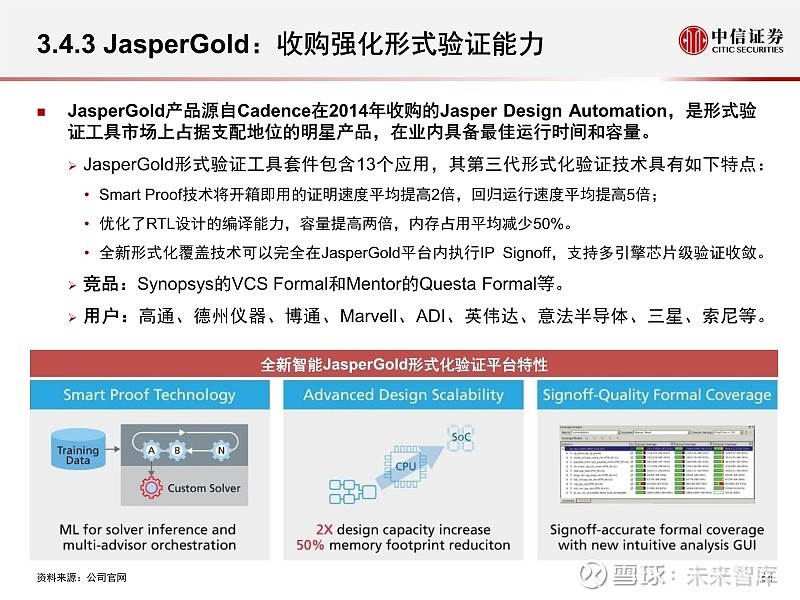

3.4.3 JasperGold:收购强化形式验证能力

JasperGold产品源自Cadence在2014年收购的Jasper Design Automation,是形式验 证工具市场上占据支配地位的明星产品,在业内具备最佳运行时间和容量。

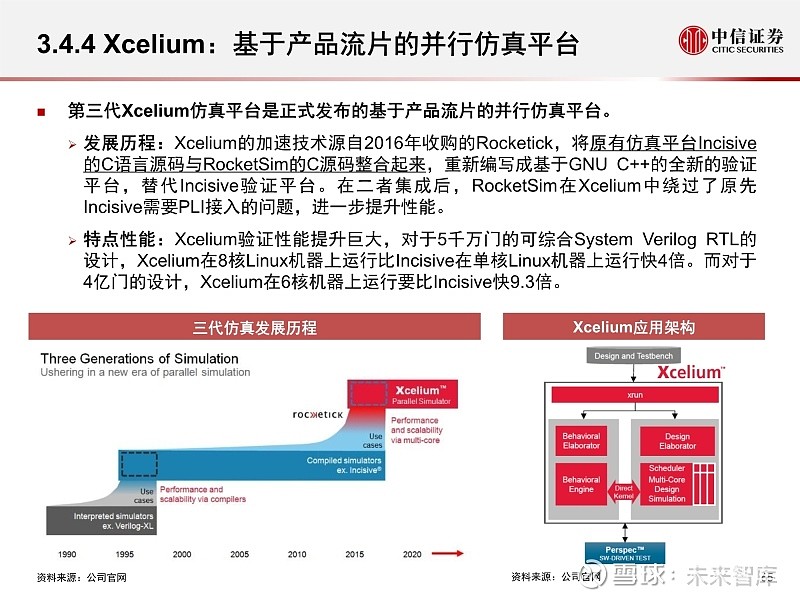

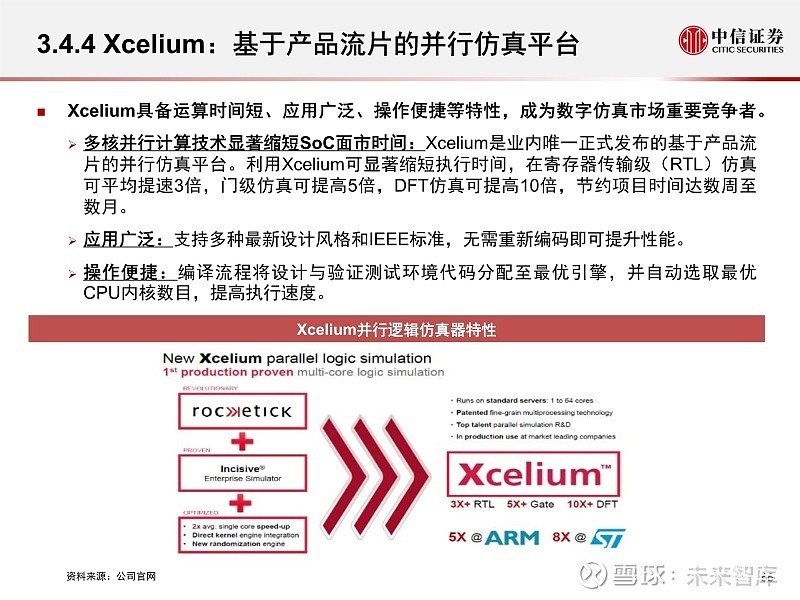

3.4.4 Xcelium:基于产品流片的并行仿真平台

第三代Xcelium仿真平台是正式发布的基于产品流片的并行仿真平台。

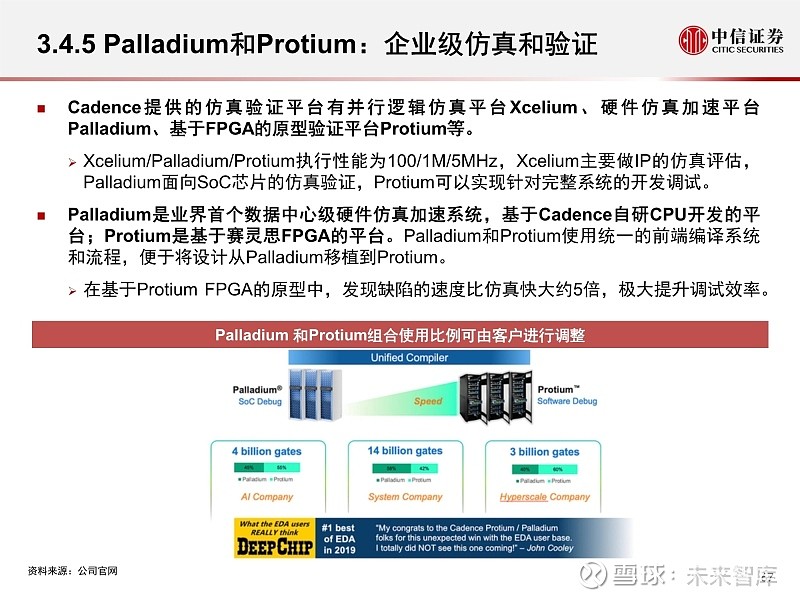

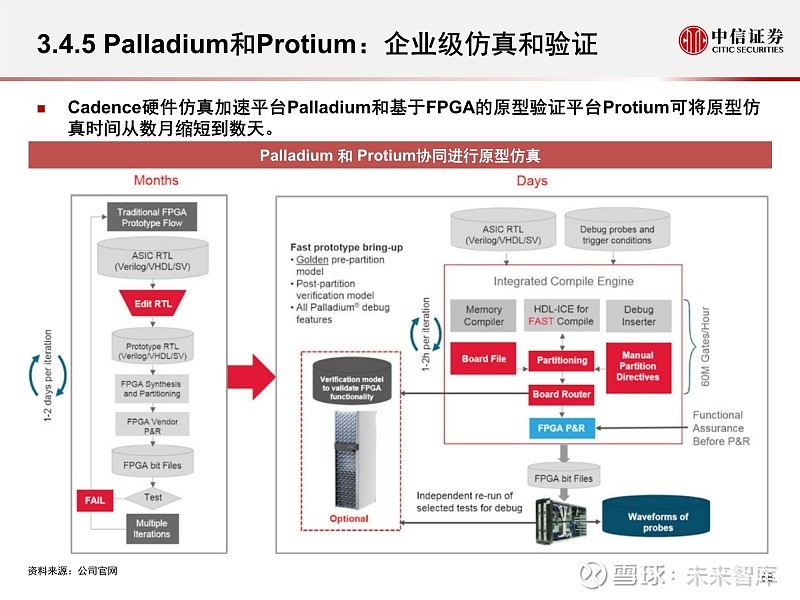

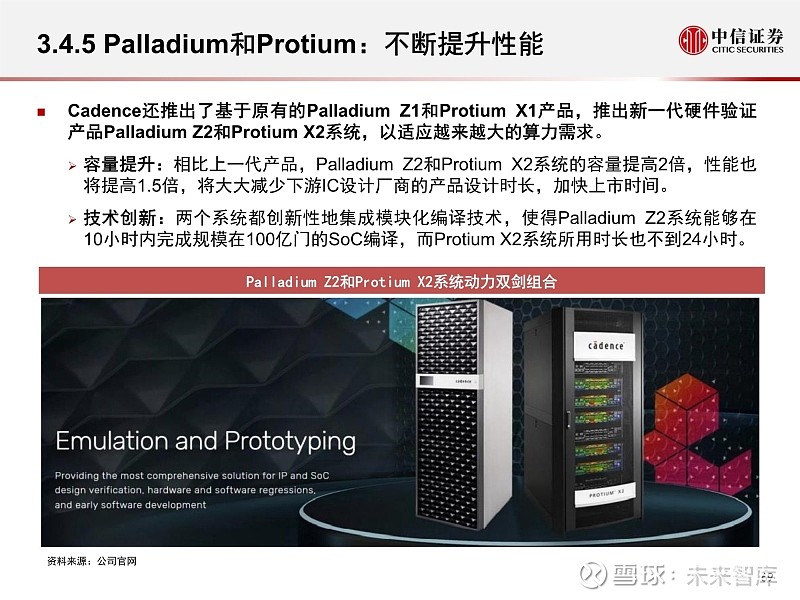

3.4.5 Palladium和Protium:企业级仿真和验证

Cadence提供的仿真验证平台有并行逻辑仿真平台 Xcelium、硬件仿真加速平台 Palladium、基于FPGA的原型验证平台Protium等。

3.5 IP核:处理器IP、设计IP、验证IP全覆盖

Cadence是增长最快的IP供应商之一,业务主要包括处理器IP、设计IP、验证IP。

3.5.1 处理器IP:涵盖可配置和可扩展的控制器和 DSP

处理器IP源自2013年收购的Tensilica,主要涵盖7大类产品,包括AI平台、雷达通信 DSP、浮点DSP、融合DSP、HiFi DSP、视觉DSP、Xtensa控制器等。

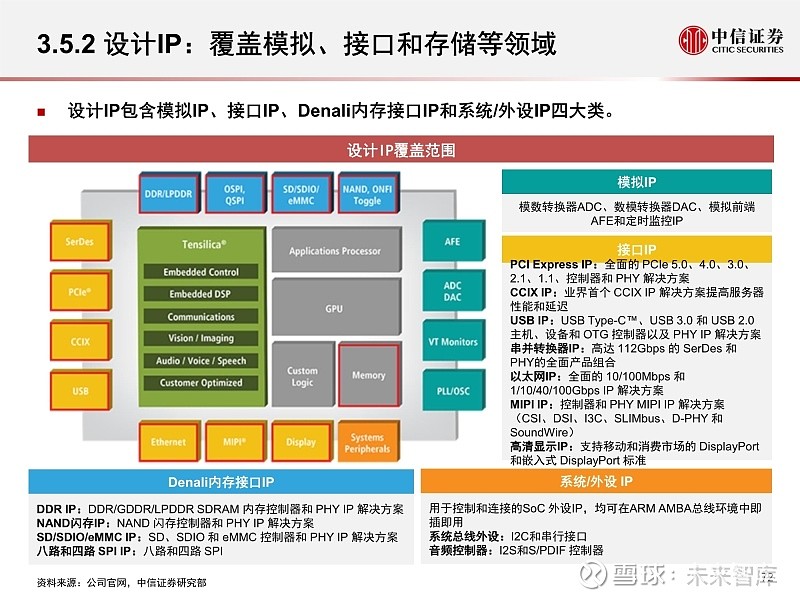

3.5.2 设计IP:覆盖模拟、接口和存储等领域

设计IP包含模拟IP、接口IP、Denali内存接口IP和系统/外设IP四大类。

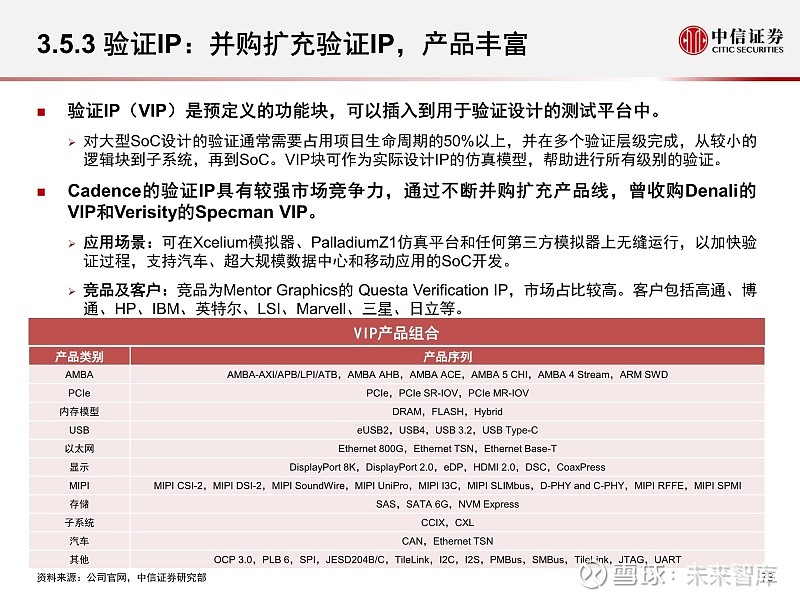

3.5.3 验证IP:并购扩充验证IP,产品丰富

验证IP(VIP)是预定义的功能块,可以插入到用于验证设计的测试平台中。

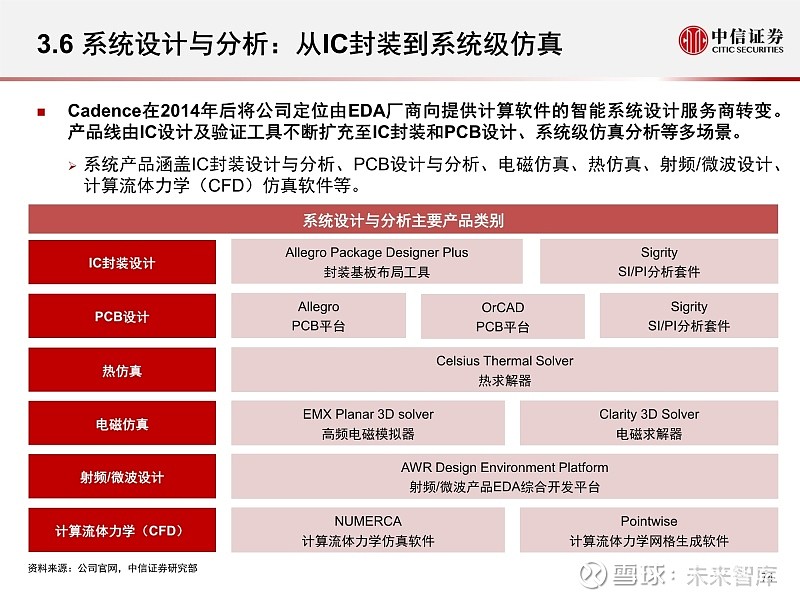

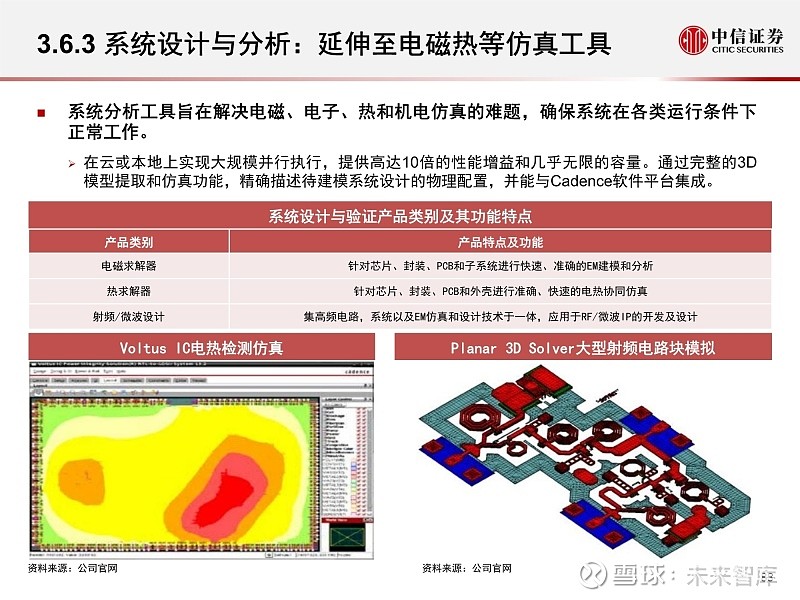

3.6 系统设计与分析:从IC封装到系统级仿真

Cadence在2014年后将公司定位由EDA厂商向提供计算软件的智能系统设计服务商转变。 产品线由IC设计及验证工具不断扩充至IC封装和PCB设计、系统级仿真分析等多场景。

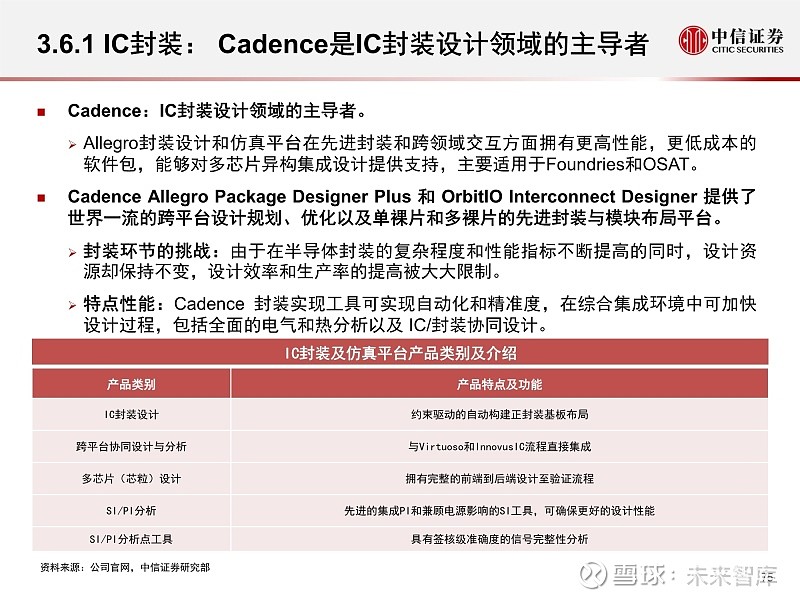

3.6.1 IC封装: Cadence是IC封装设计领域的主导者

Cadence Allegro Package Designer Plus 和 OrbitIO Interconnect Designer 提供了 世界一流的跨平台设计规划、优化以及单裸片和多裸片的先进封装与模块布局平台。

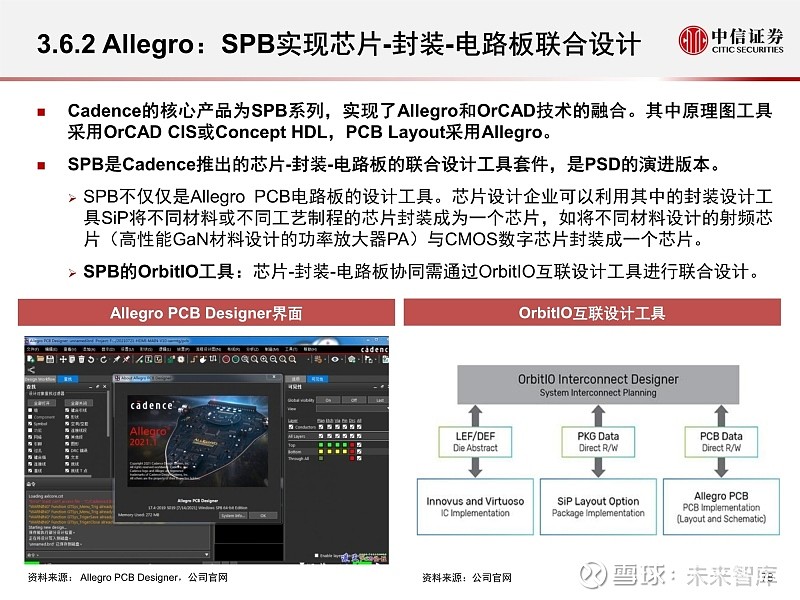

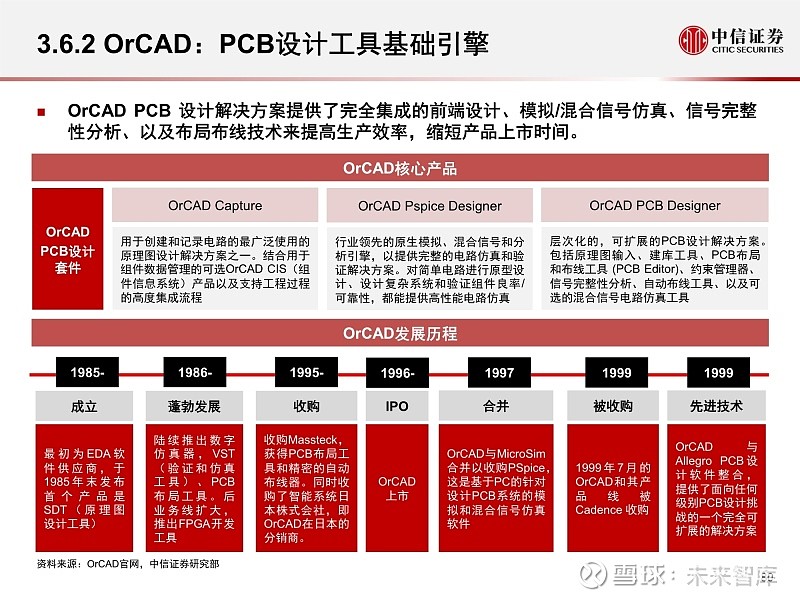

3.6.2 PCB设计分析:覆盖高中低各层次市场需求

Cadence在PCB设计领域拥有OrCAD和Allegro两类产品,目前仍执行双品牌战略。

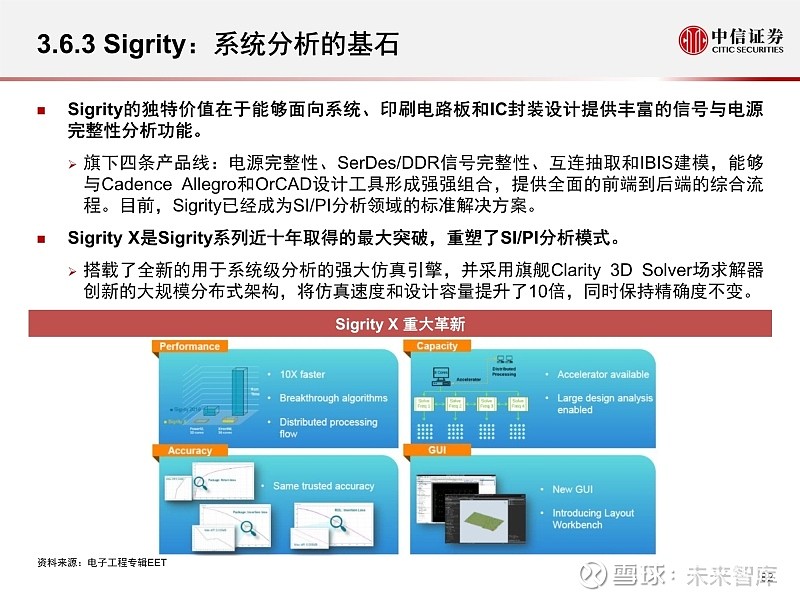

3.6.3 Sigrity:系统分析的基石

Cadence于2012年收购Sigrity,获得其SI/PI技术,融入Allegro平台中为先进封装、 PCB设计提供仿真分析途径,Sigrity是Cadence仿真业务的基石。

(获取优质报告请登录:未来智库)

四、行业启示:引领EDA发展新纪元

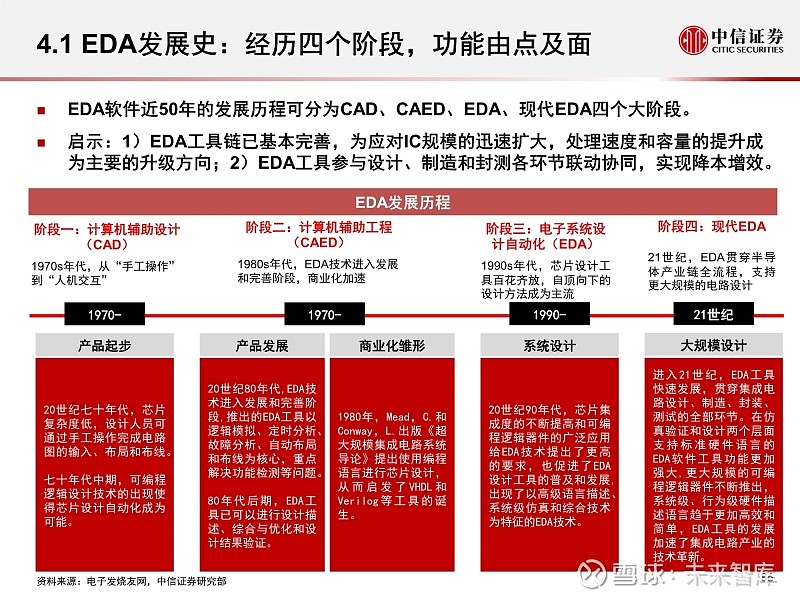

4.1 政策支持:美国政府大力扶持电子复兴计划(ERI)

美国国防部推出一项为期5年、总值15亿美元的电子复兴计划(ERI),用以支持芯片技 术的开发。美国国会也增加了对ERI的投入,每年额外注资1.5亿美元。

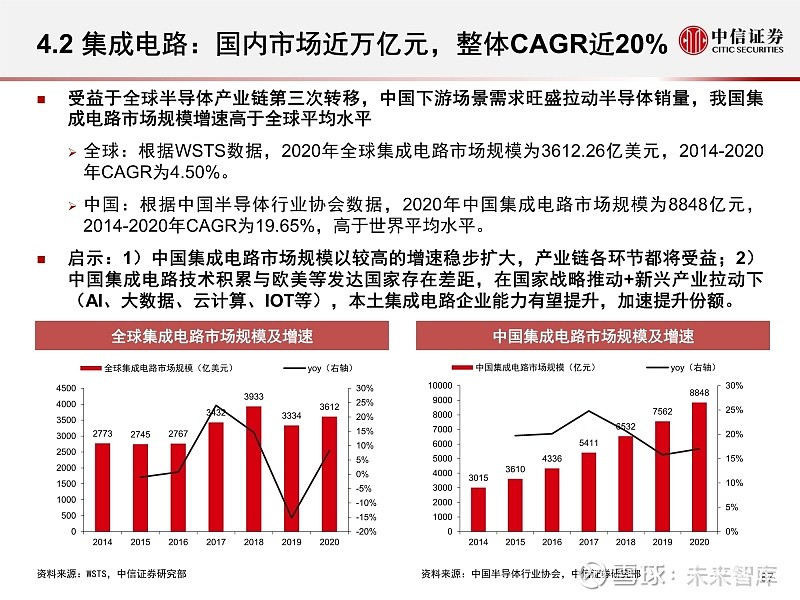

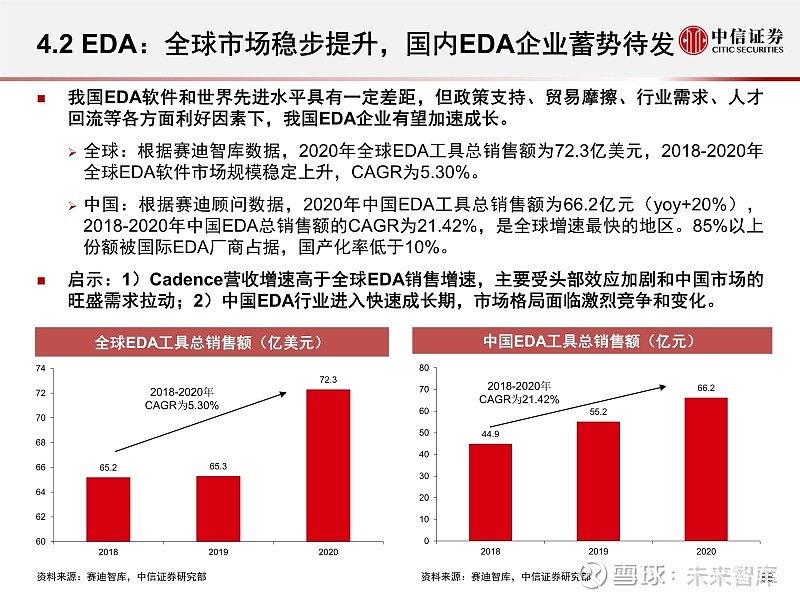

4.2 集成电路:国内市场近万亿元,整体CAGR近20%

受益于全球半导体产业链第三次转移,中国下游场景需求旺盛拉动半导体销量,我国集 成电路市场规模增速高于全球平均水平

4.3 竞争格局:国外三巨头主导

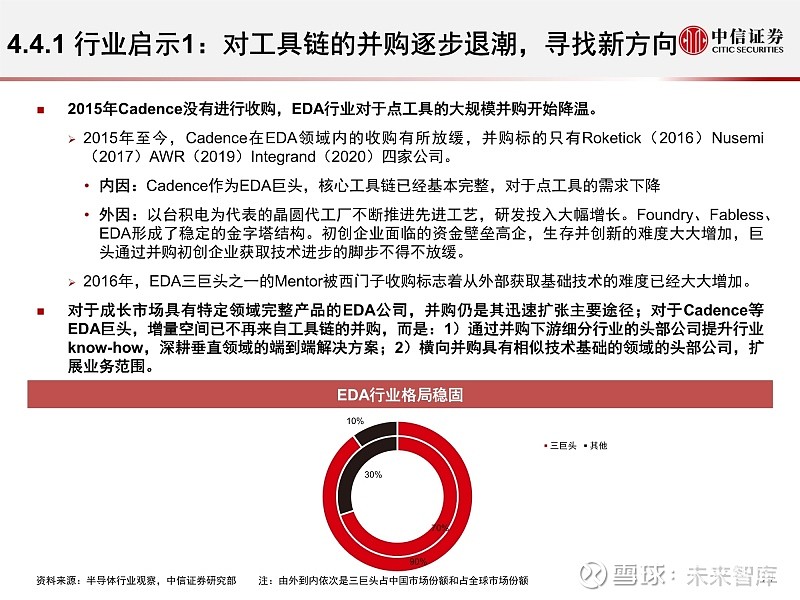

全球:Synopsis、Cadence、Siemens EDA(Mentor)三足鼎立,行业集中度高

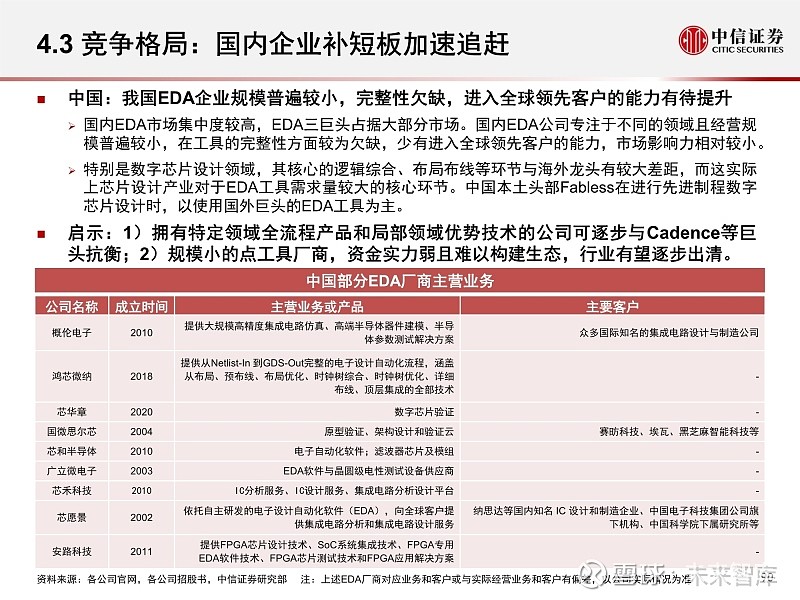

中国:我国EDA企业规模普遍较小,完整性欠缺,进入全球领先客户的能力有待提升

4.4.1 行业启示1:补全产品线是根本目的,自研+并购 是重要手段

三巨头基本实现了EDA领域的全工具链覆盖,多个拳头产品处于行业领先地位。

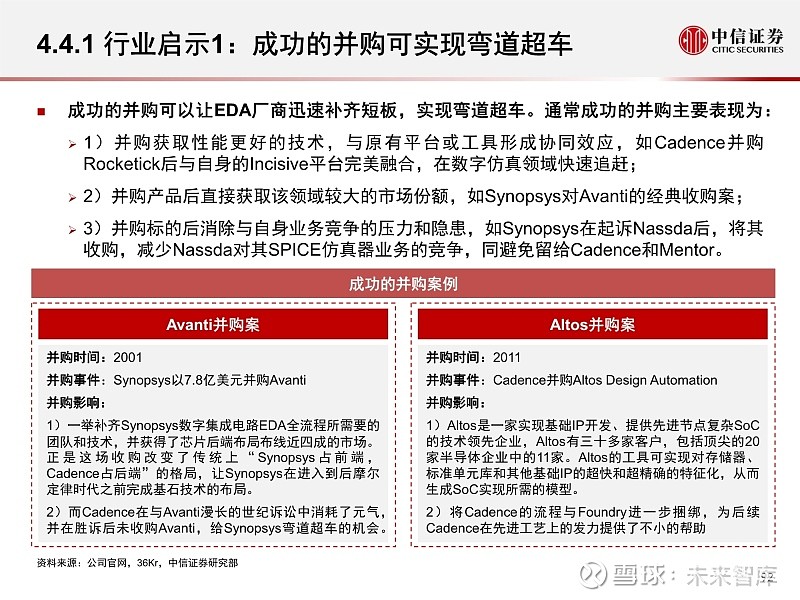

成功的并购可以让EDA厂商迅速补齐短板,实现弯道超车。

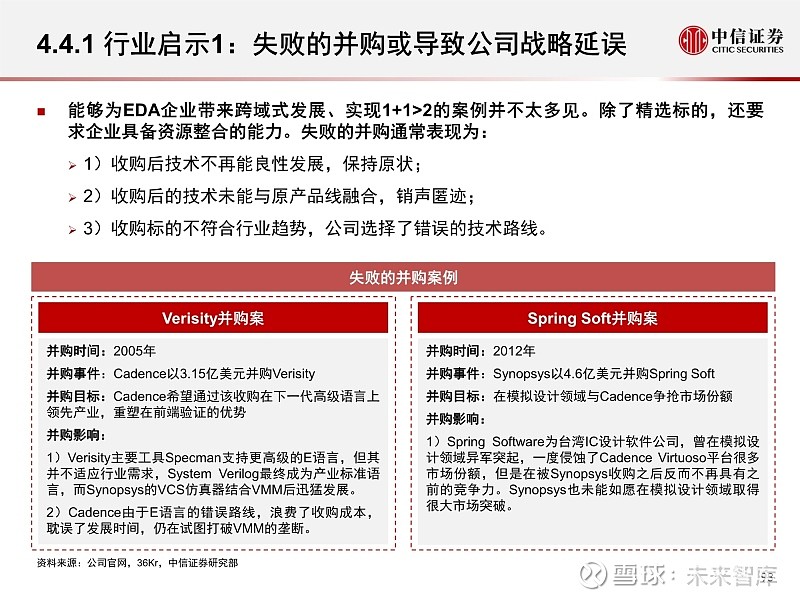

能够为EDA企业带来跨域式发展、实现1+1>2的案例并不太多见。

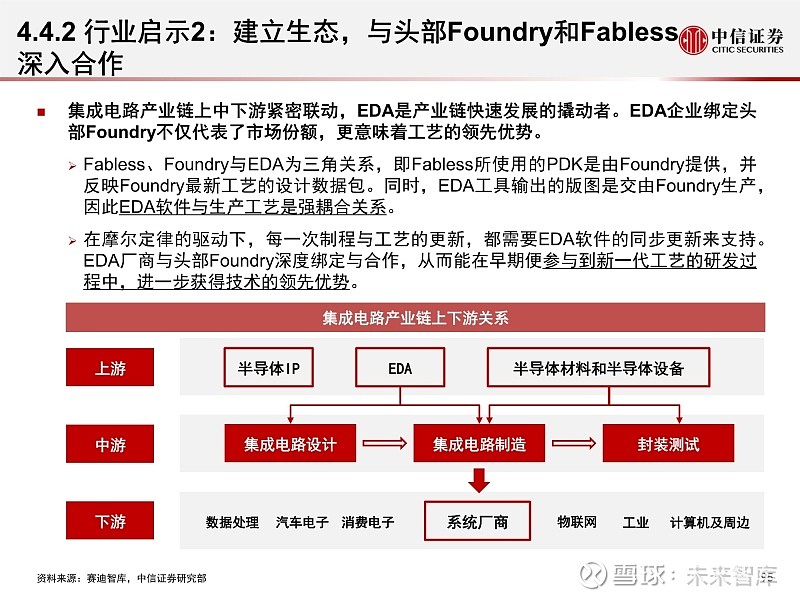

4.4.2 行业启示2:建立生态,与头部Foundry和Fabless 深入合作

集成电路产业链上中下游紧密联动,EDA是产业链快速发展的撬动者。EDA企业绑定头 部Foundry不仅代表了市场份额,更意味着工艺的领先优势。

EDA闭环工具链和IP授权的模式打造了完整的IC设计生态。

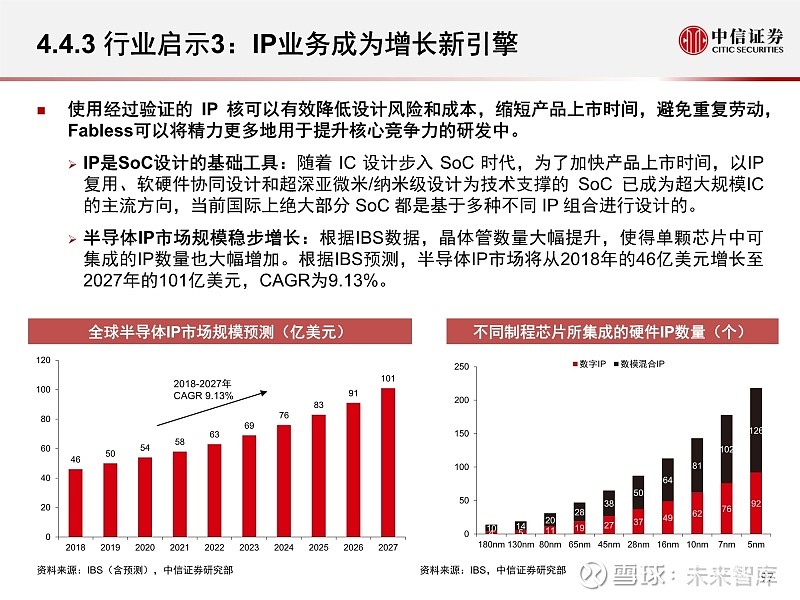

4.4.3 行业启示3:IP业务成为增长新引擎

使用经过验证的 IP 核可以有效降低设计风险和成本,缩短产品上市时间,避免重复劳动, Fabless可以将精力更多地用于提升核心竞争力的研发中。

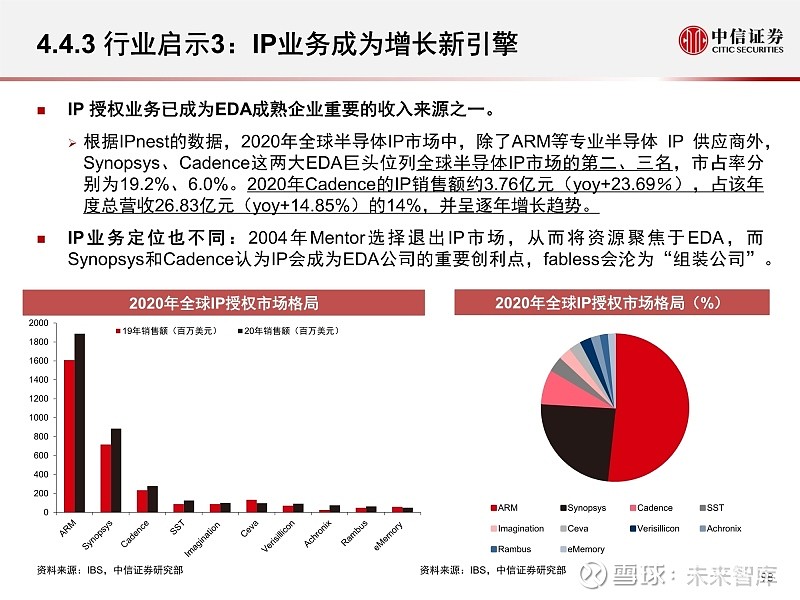

P 授权业务已成为EDA成熟企业重要的收入来源之一。

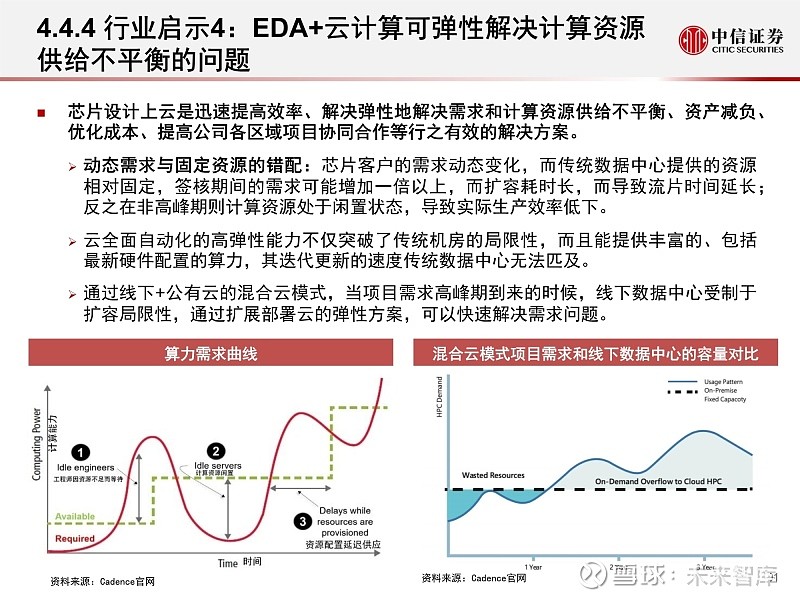

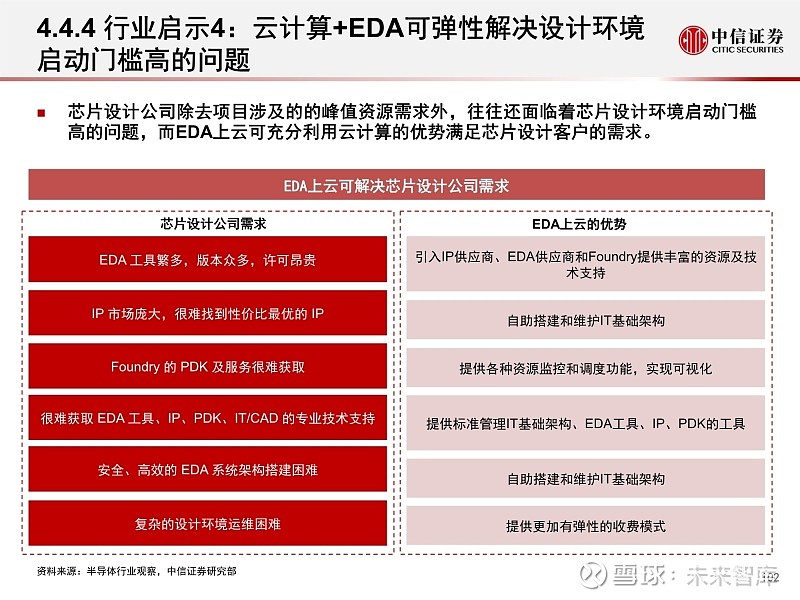

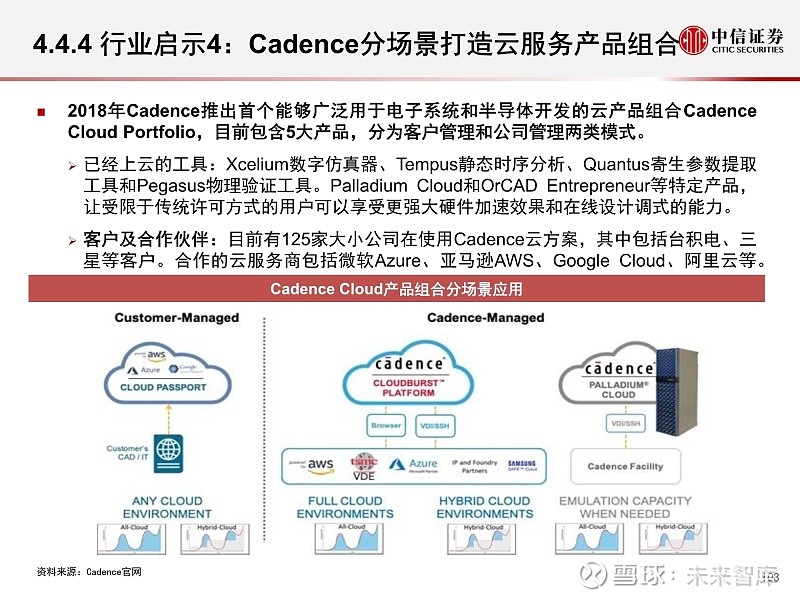

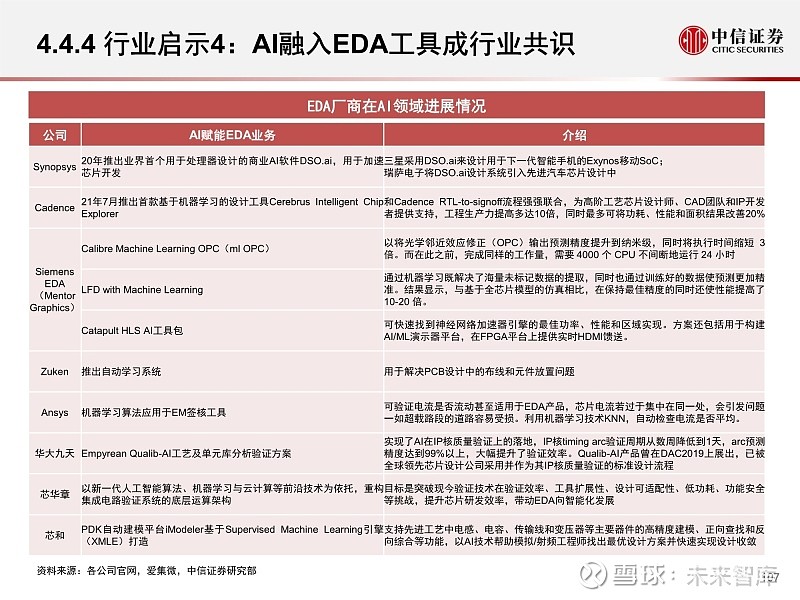

4.4.4 行业启示4:EDA上云步伐不断加快

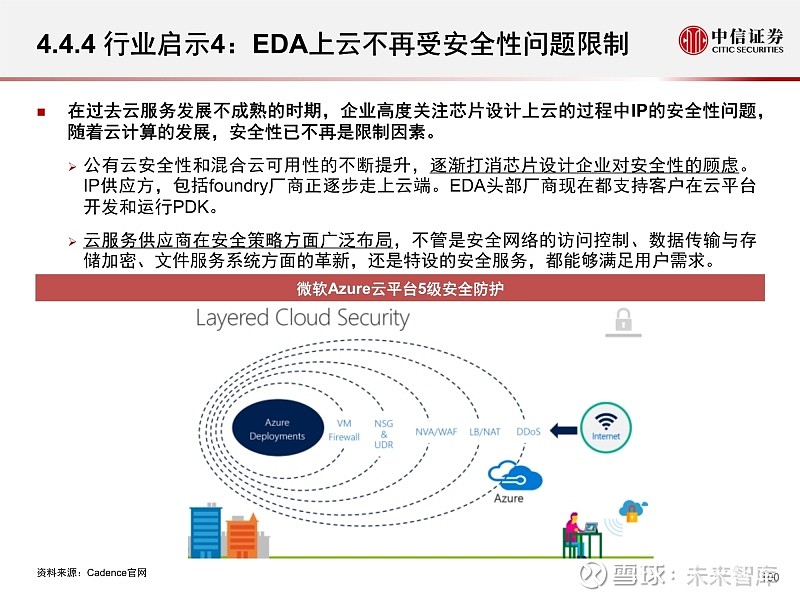

在过去云服务发展不成熟的时期,企业高度关注芯片设计上云的过程中IP的安全性问题, 随着云计算的发展,安全性已不再是限制因素。

报告节选:

(本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。)

详见报告原文。

精选报告来源:【未来智库】。